FEUL671000-01

# ML671000 Users' Manual CMOS 32-Bit Single-Chip Microcontroller

FIRST EDITION ISSUE DATE: Jul. 2001

#### NOTICE

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or applications may result in the loss or damage of property, or death or injury to humans. Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment, nuclear power control, medical equipment, and life-support systems.

- 7. Certain products in this document may need governmental approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents contained herein may be reprinted or reproduced without our prior permission.

- 9. ARM, ARM POWERED logo and Thumb are registered trademarks of ARM Limited. ARM7TDIM and Multi-ICE are trademarks of ARM Limited.

Copyright 2001 OKI ELECTRIC INDUSTRY CO., LTD.

## Preface

The ML671000 is a 32-bit CMOS single-chip microcontroller combining a 32-bit ARM7TDMI RISC CPU core developed by ARM Limited with a broad set of peripheral functions that make it ideal for controlling PC peripherals, communications terminals, and the like.

This User's Manual primarily covers the ML671000 hardware.

Application developers should also refer to the following related manuals and documents.

- ARM7TDMI Data Sheet

- ARM Software Development Toolkit User Guide

- ARM Software Development Toolkit Reference Guide

- Multi-ICE User Guide

- OKI ADI-BOARD User's Guide

- ML671000 CPU BOARD User's Guide

- CAB\_671000\_P Board Kit Printer Interface Application Manual (Sample program for USB device controller)

- USB Standard

- UNIVERSAL SERIAL BUS Specification Version 1.0

- UNIVERSAL SERIAL BUS Specification Version 1.1

This document is subject to change without notice.

# Contents

| <b>C1</b> | 4 | $\sim$ · |   |

|-----------|---|----------|---|

| Chapter   | Ι | Overviev | N |

| 1.1.  | Features            | 1-2  |

|-------|---------------------|------|

| 1.2.  | Block Diagram       | 1-4  |

|       | Pins                |      |

| 1.3.1 | 1. Pin Descriptions | 1-6  |

| 1.3.2 | 2. Pin Structure    | 1-11 |

| 1.3.3 | 3. Pin Treatment    | 1-12 |

# Chapter 2 CPU

| 2.1. Overview                                                 | 2-2  |

|---------------------------------------------------------------|------|

| 2.2. CPU Operating States                                     | 2-2  |

| 2.3. Switching State                                          | 2-2  |

| 2.4. Memory Formats                                           | 2-2  |

| 2.5. Instruction Length                                       | 2-3  |

| 2.6. Data Types                                               | 2-3  |

| 2.7. Operating Modes                                          | 2-3  |

| 2.8. Registers                                                | 2-4  |

| 2.8.1. The ARM state register set                             | 2-4  |

| 2.8.2. The Thumb state register set                           | 2-6  |

| 2.8.3. The relationship between ARM and Thumb state registers | 2-7  |

| 2.8.4. Accessing Hi registers in Thumb state                  |      |

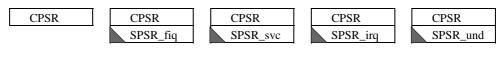

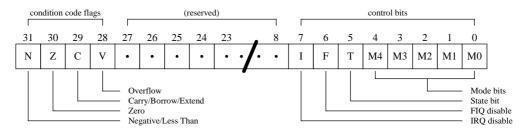

| 2.9. The Program Status Registers                             |      |

| 2.9.1. The condition code flags                               | 2-8  |

| 2.9.2. The control bits                                       |      |

| 2.10. Exceptions                                              | 2-10 |

| 2.10.1. Action on entering an exception                       | 2-10 |

| 2.10.2. Action on leaving an exception                        |      |

| 2.10.3. Exception entry/exit summary                          | 2-11 |

| 2.10.4. FIQ                                                   |      |

| 2.10.5. IRQ                                                   | 2-12 |

| 2.10.6. Software interrupt                                    | 2-12 |

| 2.10.7. Undefined instruction                                 | 2-12 |

| 2.10.8. Exception vectors                                     | 2-13 |

| 2.10.9. Exception priorities                                  |      |

| 2.11. Reset                                                   |      |

# Chapter 3 CPU Control Functions

| 3.1. C | verview                                      | 3-2 |

|--------|----------------------------------------------|-----|

| 3.1.1. | Pins                                         | 3-3 |

| 3.1.2. | Control Registers                            | 3-3 |

| 3.2. D | Petailed Control Register Descriptions       | 3-4 |

| 3.2.1. | Standby Control Register (SBYCON)            | 3-4 |

| 3.2.2. | Clock Control Register (CKCON)               | 3-5 |

| 3.2.3. | Clock Supply Wait Control Register (CKWTCON) | 3-6 |

|        | Reset Status Register (RSTST)                |     |

| 3.3. S | ystem Resets                                 | 3-8 |

| 3.3.1. | Resetting with External Input                | 3-8 |

| 3.3.2. | Resetting with Watchdog Timer Overflow       | 3-8 |

| 3.4. S | ystem Clock (SYSCLK)                         | 3-9 |

| 3.5. S | tandby Modes       |  |

|--------|--------------------|--|

|        | HALT Mode          |  |

| 3.5.2. | STOP Mode          |  |

| 3.6. C | Clock Supply Delay |  |

| Chapter 4 | Interrupt | Controller |

|-----------|-----------|------------|

| Chapter + | micrupi   | Controller |

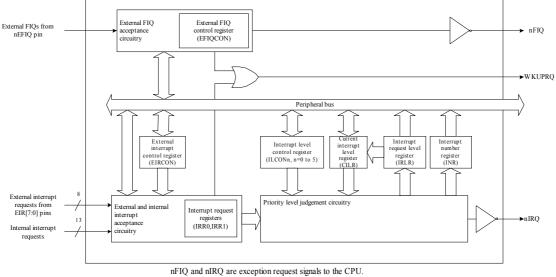

| 4.1. Overview                                                      |

|--------------------------------------------------------------------|

| 4.1.1. Block Diagram                                               |

| 4.1.2. Pins                                                        |

| 4.1.3. Control Registers                                           |

| 4.2. Interrupt Sources                                             |

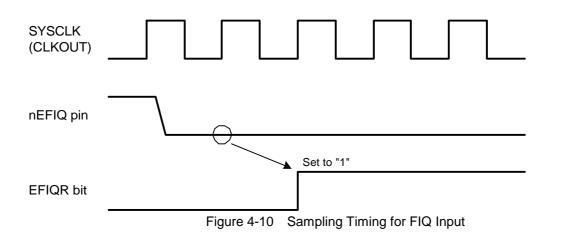

| 4.2.1. External FIQ Interrupt Requests                             |

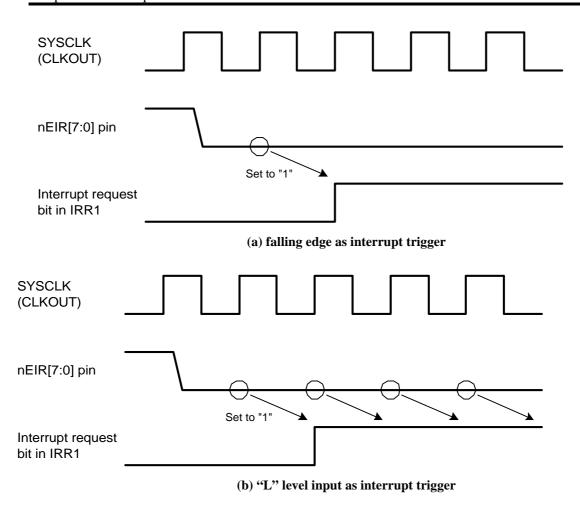

| 4.2.2. External Interrupt Requests                                 |

| 4.2.3. Internal Interrupt Requests                                 |

| 4.2.4. Interrupt Sources, Interrupt Numbers, and Control Registers |

| 4.3. Detailed Control Register Descriptions                        |

| 4.3.1. Interrupt Number Register (INR)                             |

| 4.3.2. Current Interrupt Level Register (CILR)                     |

| 4.3.3. Interrupt Request Level Register (IRLR)                     |

| 4.3.4. External FIQ Control Register (EFIQCON)                     |

| 4.3.5. External Interrupt Control Register (EIRCON)                |

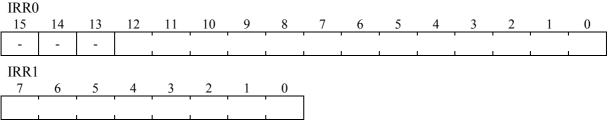

| 4.3.6. Interrupt Request Registers (IRR0 and IRR1)                 |

| 4.3.7. Interrupt Level Control Registers (ILCONn, n=0 to 5)        |

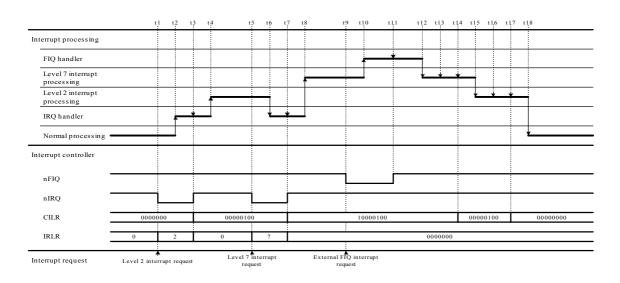

| 4.4. Interrupt Processing                                          |

| 4.4.1. External FIQ Interrupts                                     |

| 4.4.1.1. Interrupt Sequence                                        |

| 4.4.2. External and Internal Interrupts4-13                        |

| 4.4.2.1. Interrupt Priority Levels                                 |

| 4.4.2.2. Interrupt Sequence                                        |

| 4.4.2.3. Interrupt Level Control Example                           |

| 4.5. Sampling Timing for External Interrupt Requests               |

| 4.6. Interrupt Latency                                             |

| 4.7. Notes on Processing Interrupts                                |

# Chapter 5 I/O Ports

| Overview                                              |                                                           |

|-------------------------------------------------------|-----------------------------------------------------------|

| 1. Control Registers                                  |                                                           |

| Detailed Control Register Descriptions                |                                                           |

| 1. Port Output Registers (POn, n=0 to 3)              |                                                           |

| 2. Port Input Registers (PIn, n=0 to 3)               |                                                           |

| 3. Port Mode Registers (PMn, n=0 to 3)                |                                                           |

| 4. Port Function Selection Registers (PFSn, n=0 to 3) | 5-8                                                       |

|                                                       | <ol> <li>Detailed Control Register Descriptions</li></ol> |

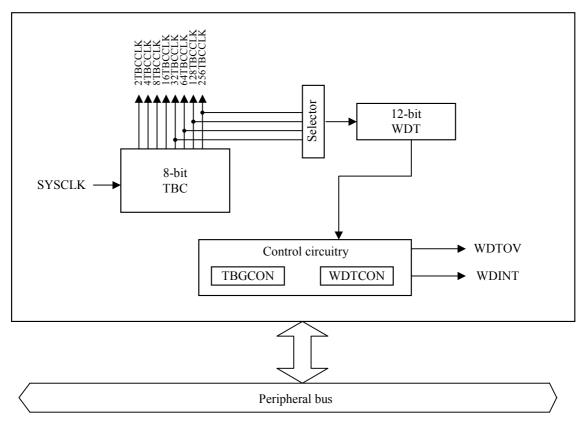

# Chapter 6 Time Base Generator

| 6.1. Overview                                   | 6-2 |

|-------------------------------------------------|-----|

| 6.1.1. Block Diagram                            |     |

| 6.1.2. Control Registers                        |     |

| 6.2. Detailed Control Register Descriptions     |     |

| 6.2.1. Watchdog Timer Control Register (WDTCON) | 6-4 |

| 6.2.2. Time Base Control Register (TBGCON)      | 6-5 |

| 6.3. Time Base Generator Operation              | 6-6 |

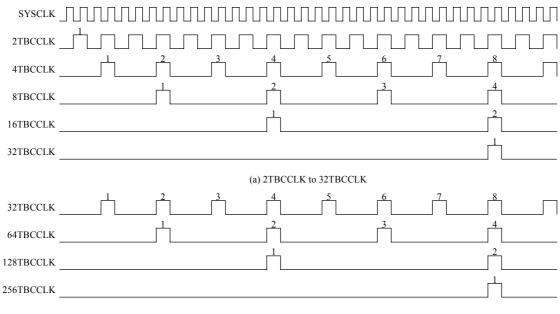

| 6.3.1. Time Base Counter (TBC)                  | 6-6 |

|                                                 |     |

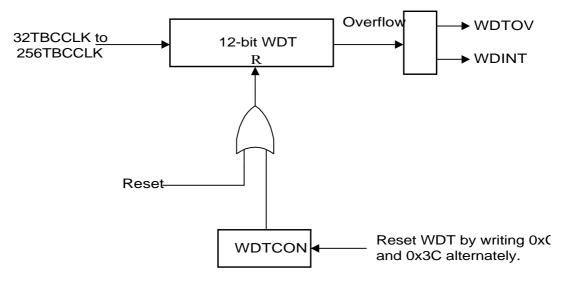

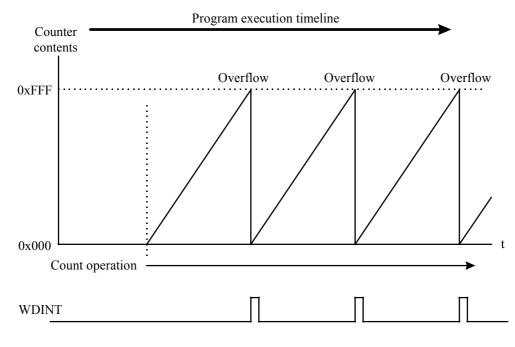

| 6.3.2. | Watchdog Timer (WDT)                    | 6-7  |

|--------|-----------------------------------------|------|

|        | Watchdog Timer Overflow Interval (tWDT) |      |

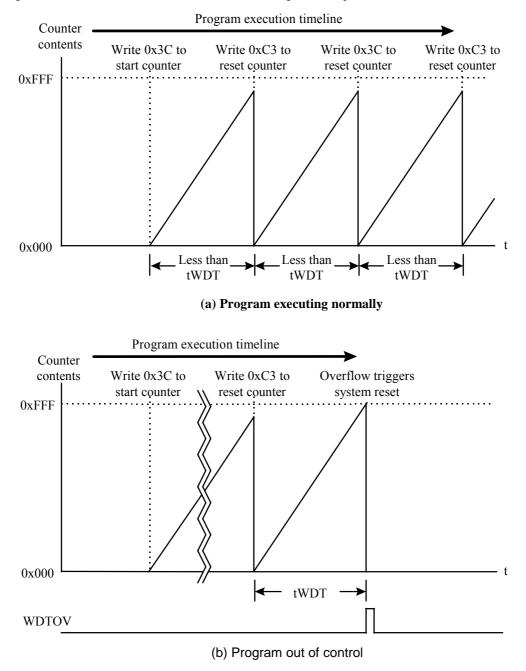

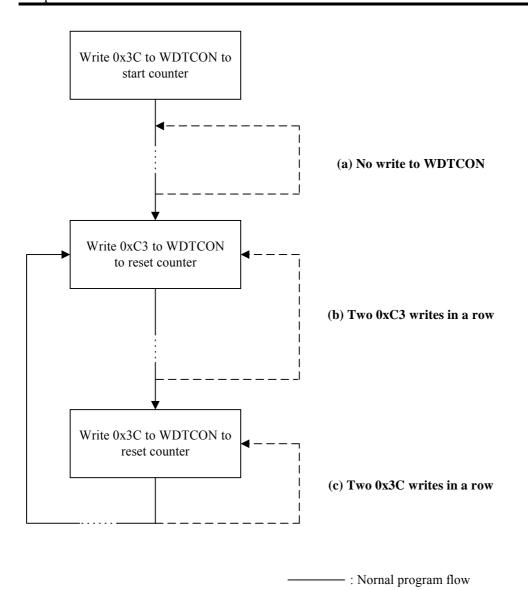

| 6.3.4. | Watchdog Timer Operation                | 6-9  |

| 6.3.5. | Interval Timer Operation                | 6-11 |

# Chapter 7 Timers

| 71 0    | verview                                                    |

|---------|------------------------------------------------------------|

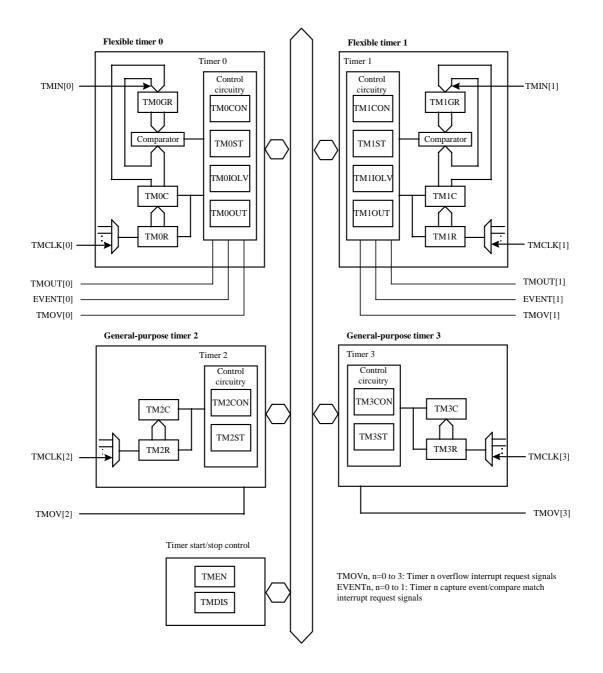

| 7.1.1.  | Block Diagram                                              |

| 7.1.2   | Pins                                                       |

| 7.1.3.  |                                                            |

|         | etailed Control Register Descriptions                      |

| 7.2.1.  | Flexible Timer Control Registers (TMnCON, n=0 to 1)        |

| 7.2.2.  | General-Purpose Timer Control Registers (TMnCON, n=2 to 3) |

| 7.2.3.  | Flexible Timer Status Registers (TMnST, n=0 to 1)          |

| 7.2.4.  | General-Purpose Timer Status Registers (TMnST, n=2 to 3)   |

| 7.2.5.  | Timer Counters (TMnC, n=0 to 3)                            |

| 7.2.6.  | Timer Registers (TMnC, n=0 to 3)                           |

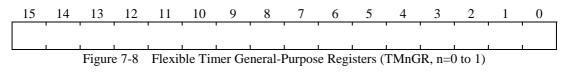

| 7.2.7.  | Flexible Timer General-Purpose Registers (TMnGR, n=0 to 1) |

| 7.2.8.  | Flexible Timer I/O Level Registers (TMnIOV, n=0 to 1)      |

| 7.2.9.  | Flexible Timer Output Registers (TMnOUT, n=0 to 1)         |

| 7.2.10. |                                                            |

| 7.2.11. | Timer Disable Register (TMDIS)                             |

|         | mer Operation                                              |

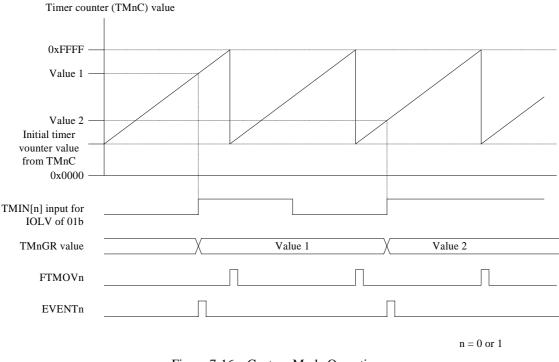

| 7.3.1.  | Flexible Timer Operation                                   |

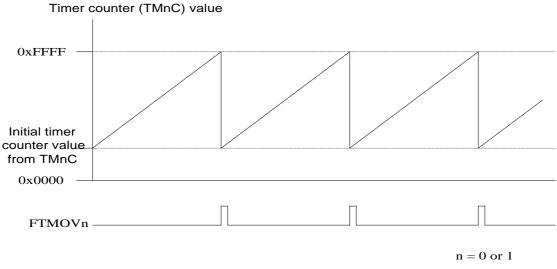

| 7.3.1   | .1. Auto Reload Timer Mode                                 |

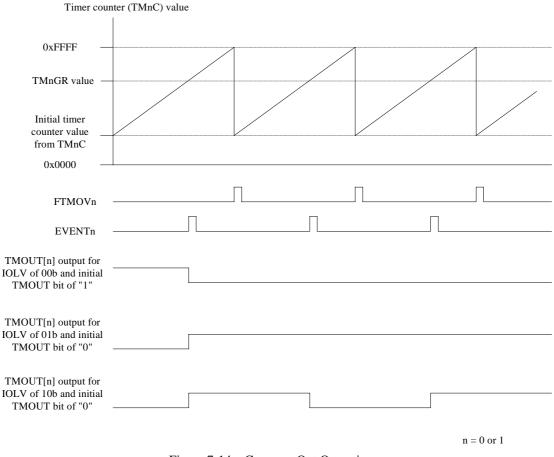

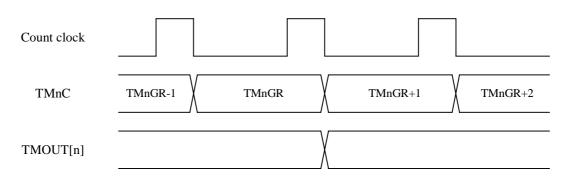

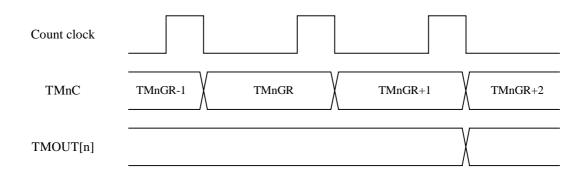

| 7.3.1   | .2. Compare Out Mode                                       |

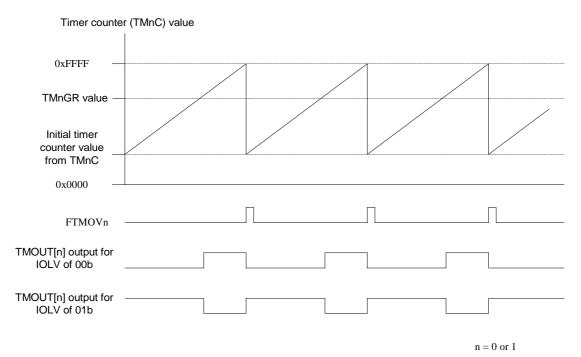

| 7.3.1   | .3. Pulse Width Modulation (PWM) Mode                      |

| 7.3.1   | .4. Capture Mode                                           |

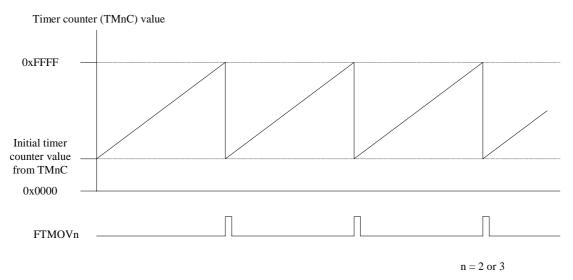

| 7.3.2.  | General-Purpose Timer Operation                            |

| 7.3.3.  | Selecting Clock                                            |

| 7.3.4.  | Starting/Stopping Timer                                    |

| 7.4. Ti | mer I/O Timing7-20                                         |

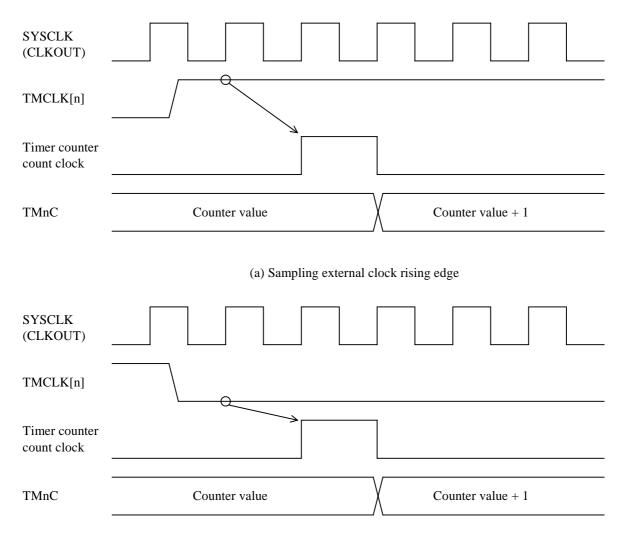

| 7.4.1.  | Sampling External Clock Signal                             |

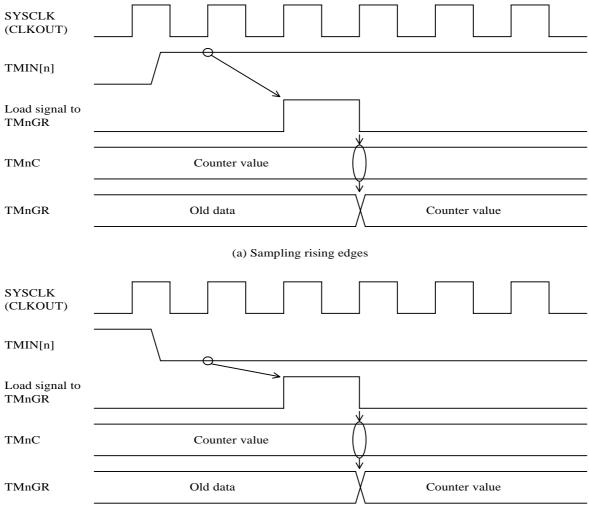

| 7.4.2.  | Sampling Capture Trigger Input                             |

| 7.4.3.  | Timer Output Timing                                        |

|         |                                                            |

# Chapter 8 Universal Asynchronous Receiver/Transmitter (UART)

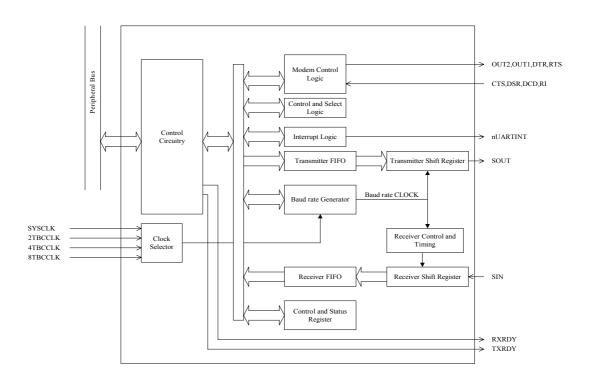

| 8.1. Overview                                  |  |

|------------------------------------------------|--|

| 8.1.1. Block Diagram                           |  |

| 8.1.2. Pins                                    |  |

| 8.1.3. Control Registers                       |  |

| 8.2. Detailed Control Register Descriptions    |  |

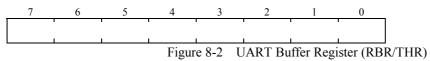

| 8.2.1. UART Buffer Register (RBR/THR)          |  |

| 8.2.2. UART Shift Registers (TSR and RSR)      |  |

| 8.2.3. FIFO Control Register (FCR)             |  |

| 8.2.4. Line Control Register (LCR)             |  |

| 8.2.5. Line Status Register (LSR)              |  |

| 8.2.6. Modem Control Register (MCR)            |  |

| 8.2.7. Modem Status Register (MSR)             |  |

| 8.2.8. Scratch Pad Register (SCR)              |  |

| 8.2.9. Interrupt Identification Register (IIR) |  |

| 8.2.10. Interrupt Enable Register (IER)        |  |

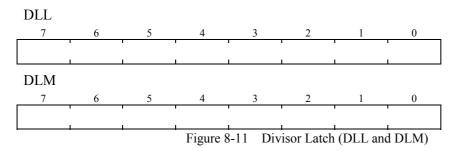

| 8.2.11. Divisor Latch (DLL and DLM)            |  |

| 8.2.12. Clock Select Register (CSR)       | 8-20 |

|-------------------------------------------|------|

| 8.3. Interrupts during Buffered Operation |      |

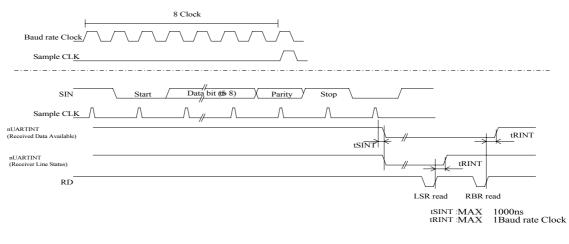

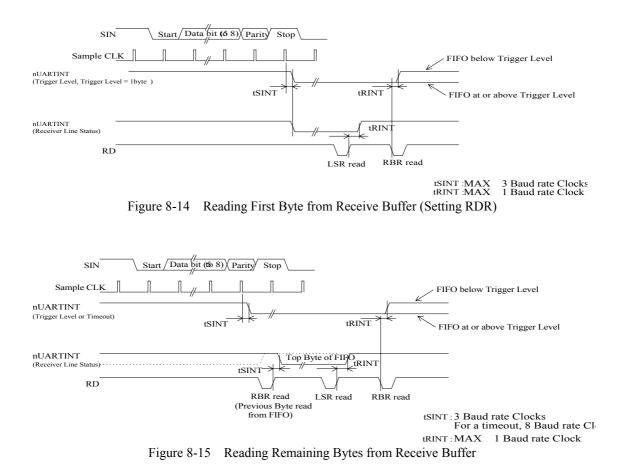

| 8.3.1. Receive Interrupts                 |      |

| 8.3.2. Transmit Interrupts                |      |

| 8.4. Polled Operation                     |      |

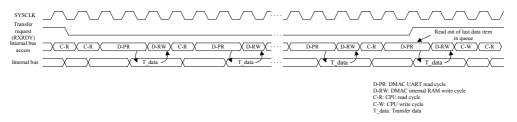

| 8.5. DMA Transfer Requests                |      |

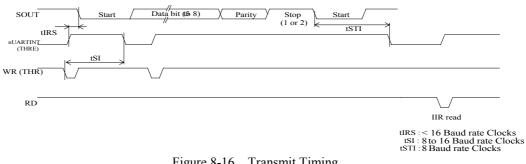

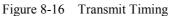

| 8.5.1. TXRDY                              |      |

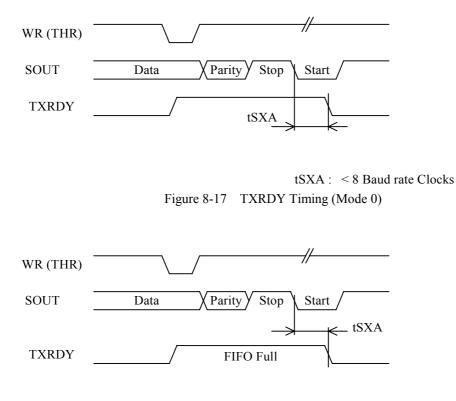

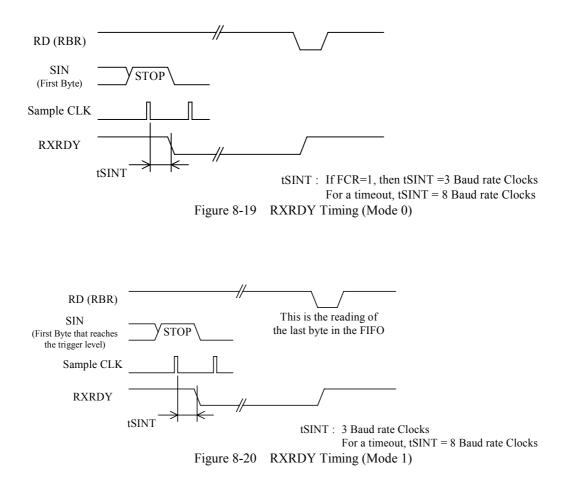

| 8.5.2. RXRDY                              |      |

|                                           |      |

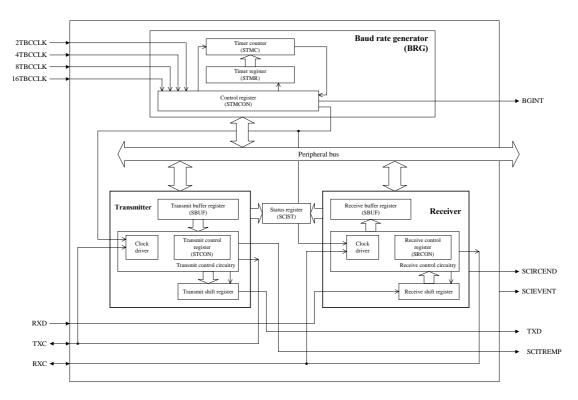

## Chapter 9 Serial Communications Interface (SCI)

| 9.1. Overview                                | 9-2  |

|----------------------------------------------|------|

| 9.1.1. Block Diagram                         | 9-3  |

| 9.1.2. Pins                                  |      |

| 9.1.3. Control Registers                     | 9-4  |

| 9.2. Detailed Control Register Descriptions  | 9-5  |

| 9.2.1. SCI Transmit Control Register (STCON) | 9-5  |

| 9.2.2. SCI Receive Control Register (SRCON)  | 9-6  |

| 9.2.3. SCI Status Register (SCIST)           | 9-7  |

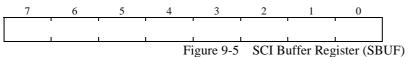

| 9.2.4. SCI Buffer Register (SBUF)            | 9-8  |

| 9.2.5. SCI Shift Registers                   | 9-8  |

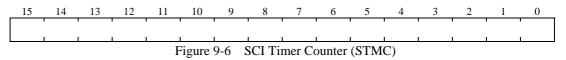

| 9.2.6. SCI Timer Counter (STMC)              | 9-8  |

| 9.2.7. SCI Timer Register (STMR)             | 9-9  |

| 9.2.8. SCI Timer Control Register (STMCON)   | 9-9  |

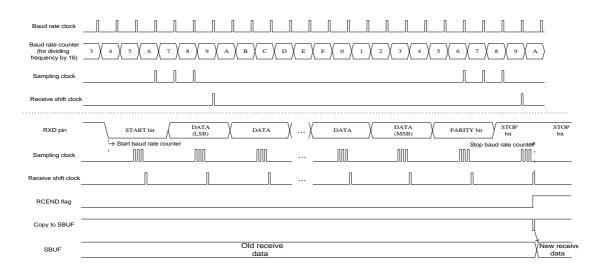

| 9.3. Asynchronous (ASI) Operation            | 9-10 |

| 9.3.1. Calculating Baud Rate                 | 9-10 |

| 9.3.2. Frame Formats                         | 9-11 |

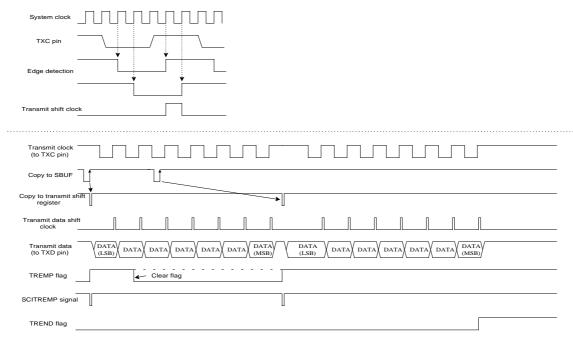

| 9.3.3. Transmitting Data                     |      |

| 9.3.4. Receiving Data                        |      |

| 9.4. Clock Synchronous (CSI) Operation       | 9-14 |

| 9.4.1. Frame Formats                         | 9-14 |

| 9.4.2. Transmitting Data                     | 9-14 |

| 9.4.2.1. Transmitting as Master              | 9-15 |

| 9.4.2.2. Transmitting as Slave               | 9-16 |

| 9.4.3. Receiving Data                        | 9-17 |

| 9.4.3.1. Receiving as Master                 |      |

| 9.4.3.2. Receiving as Slave                  | 9-18 |

|                                              |      |

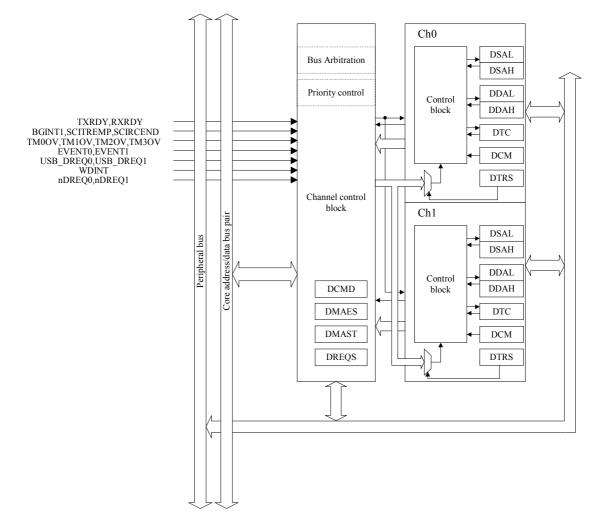

# Chapter 10 Direct Memory Access Controller (DMAC)

| 10.1. Overview                                               |  |

|--------------------------------------------------------------|--|

| 10.1.1. Block Diagram                                        |  |

| 10.1.2. Pins                                                 |  |

| 10.1.3. Control Registers                                    |  |

| 10.2. Detailed Control Register Descriptions                 |  |

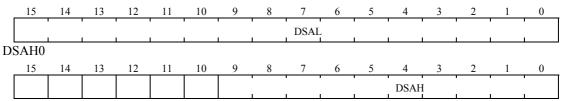

| 10.2.1. DMA Source Address Register 0 (DSAL0 and DSAH0)      |  |

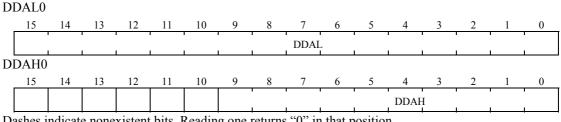

| 10.2.2. DMA Destination Address Register 0 (DDAL0 and DDAH0) |  |

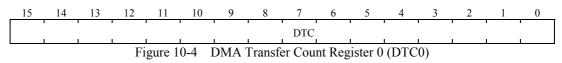

| 10.2.3. DMA Transfer Count Register 0 (DTC0)                 |  |

| 10.2.4. DMA Transfer Request Select Register 0 (DTRS0)       |  |

| 10.2.5. DMA Channel Mode Register 0 (DCM0)                   |  |

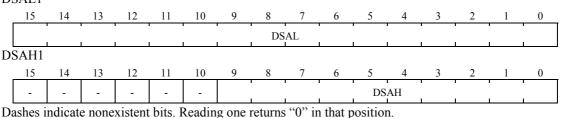

| 10.2.6. DMA Source Address Register 1 (DSAL1 and DSAH1)      |  |

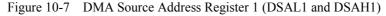

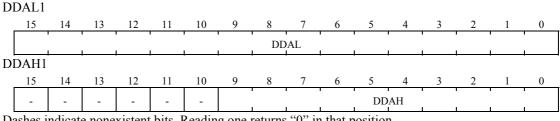

| 10.2.7. DMA Destination Address Register 1 (DDAL1 and DDAH1) |  |

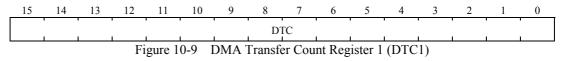

| 10.2.8. DMA Transfer Count Register 1 (DTC1)                 |  |

| 10.2.9. DMA Transfer Request Select Register 1 (DTRS1)       |  |

| 10.2.10. DMA Channel Mode Register 1 (DCM1)                  |  |

|                                                              |  |

| 10.2.11. DMA Command Register (DCMD)          |       |

|-----------------------------------------------|-------|

| 10.2.12. DMA End Status Register (DMAEST)     |       |

| 10.2.13. DMA Status Register (DMAST)          |       |

| 10.2.14. DMA Request Status Register (DREQST) |       |

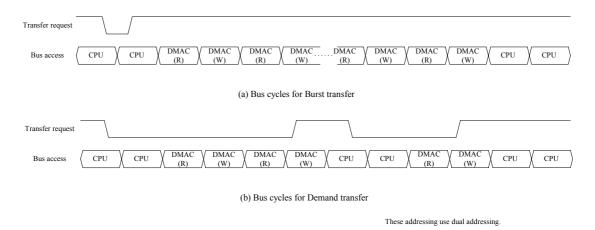

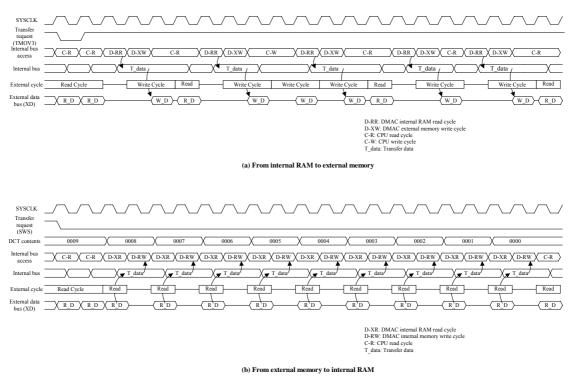

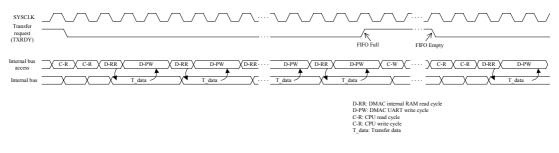

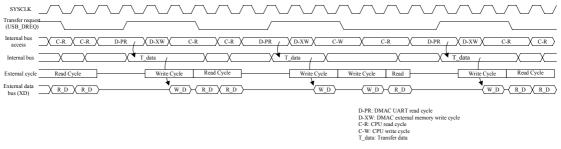

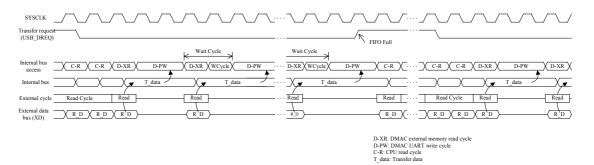

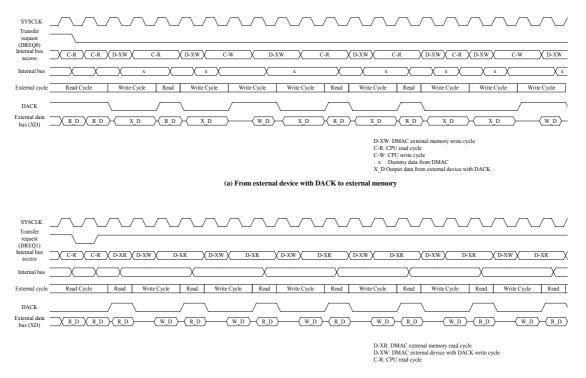

| 10.3. Operational Description                 | 10-18 |

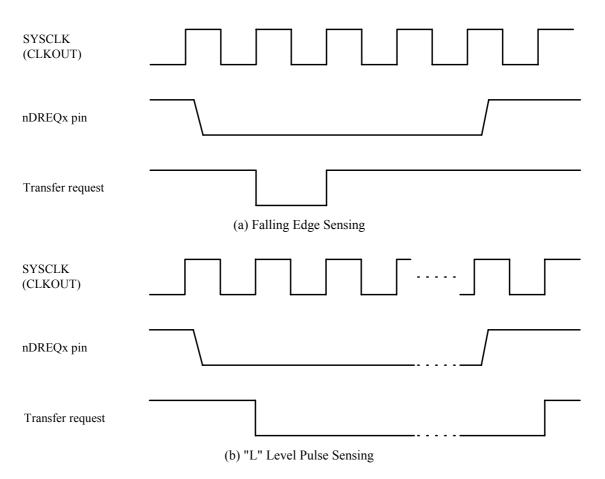

| 10.3.1. Transfer Requests                     |       |

| 10.3.2. Addressing Mode                       |       |

| 10.3.3. Transfer Modes                        |       |

| 10.3.4. Access Data Sizes                     |       |

| 10.3.5. Channel Priority Order                |       |

| 10.3.6. DMA Transfer End Conditions           |       |

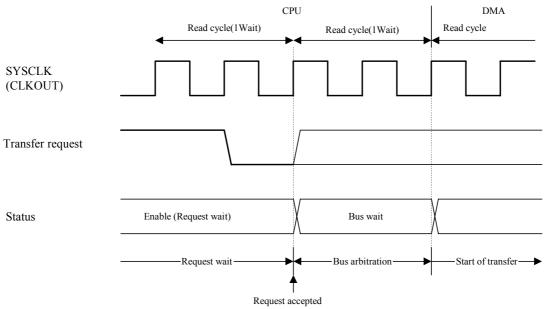

| 10.4. DMA Transfer Timing                     |       |

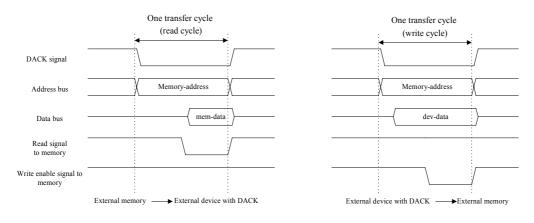

| 10.4.1. DMA Transfer Start Timing             |       |

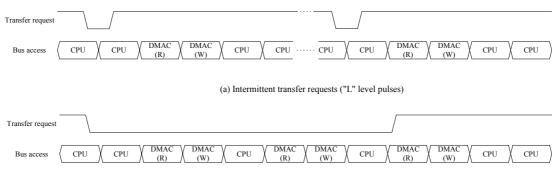

| 10.4.2. Examples of DMA transfer timing       |       |

| 10.5. Usage Notes                             |       |

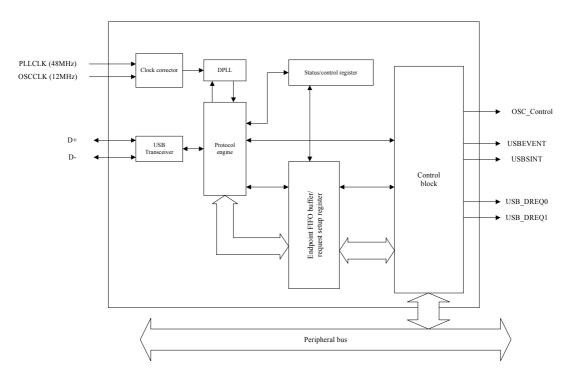

## Chapter 11 Universal Serial Bus Device Controller (USBC)

| 11.1. Ov | verview                                                  | -2 |

|----------|----------------------------------------------------------|----|

| 11.1.1.  | Block Diagram                                            | -3 |

| 11.1.2.  | Pins                                                     | -4 |

| 11.1.3.  | Control Registers                                        | -4 |

| 11.2. De | tailed Control Register Descriptions11                   | -6 |

| 11.2.1.  | Device Address Register (DVCADR)                         | -6 |

| 11.2.2.  | Device Status Register (DVCSTAT)11-                      | -6 |

|          | Packet Error Register (PKTERR)11-                        |    |

|          | FIFO Status Registers (FIFOSTATn, n=1 to 2)11-           |    |

| 11.2.5.  | Frame Number Register Pair (FRAMEMSB and FRAMELSB)11-    | -9 |

|          | Endpoint Packet Ready Register (PKTRDY)11-1              |    |

| 11.2.7.  | Endpoint 0 Receive Byte Count Register (EP0RXCNT)11-1    | 12 |

|          | Endpoint 1 Receive Byte Count Register (EP1RXCNT)11-1    |    |

| 11.2.9.  | Endpoint 2 Receive Byte Count Register (EP2RXCNT)11-1    | 13 |

| 11.2.10  | . Endpoint 3 Receive Byte Count Register Pair            |    |

|          | (EP3RXCNTMSB and EP3RXCNTLSB)11-1                        |    |

| 11.2.11  | . Transmit FIFO Buffer Clear Register (CLRFIFO)11-1      | 15 |

|          | . Software Reset Register (SOFTRST)11-1                  |    |

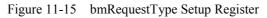

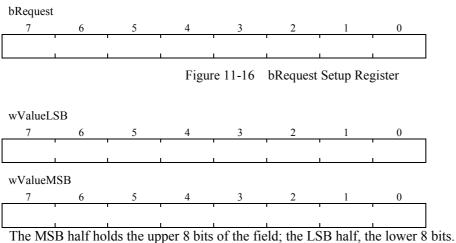

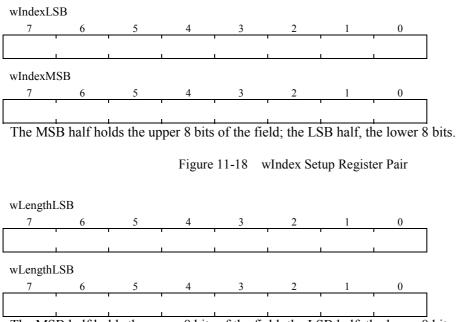

|          | .Request Setup Registers11-1                             |    |

|          | . Interrupt Enable Registers (INTENBLn, n=1 to 2)11-1    |    |

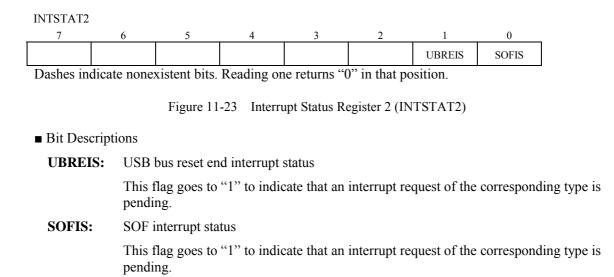

|          | . Interrupt Status Registers (INTSTATn, n=1 to 2)11-1    |    |

|          | . Endpoint 2 DMA Control Register (DMACON2)11-2          |    |

|          | . Endpoint 2 DMA Interval Register (DMAINTVL2)11-2       |    |

|          | . Endpoint 3 DMA Control Register (DMACON3)11-2          |    |

|          | . Endpoint 3 DMA Interval Register (DMAINTVL3)11-2       |    |

|          | . Endpoint 0 Receive Control Register (EP0RXCON)11-2     |    |

|          | . Endpoint 0 Receive Data Toggle Register (EP0RXTGL)11-2 |    |

|          | . Endpoint 0 Receive Payload Register (EP0RXPLD)11-2     |    |

|          | . Endpoint 1 Control Register (EP1CON)11-2               |    |

|          | . Endpoint 1 Data Toggle Register (EP1TGL)11-2           |    |

|          | . Endpoint 1 Payload Register (EP1PLD)11-2               |    |

|          | . Endpoint 0 Transmit Control Register (EP0TXCON)11-2    |    |

|          | . Endpoint 0 Transmit Data Toggle Register (EP0TXTGL)    |    |

|          | . Endpoint 0 Transmit Payload Register (EP0TXPLD)11-2    |    |

|          | . Endpoint 0 Status Register (EP0STAT)11-2               |    |

|          | . Endpoint 2 Control Register (EP2CON)11-3               |    |

| 11.2.31  | . Endpoint 2 Data Toggle Register (EP2TGL)11-3           | 31 |

| 11.2.32. Endpoint 2 Payload Register (EP2PLD)                       |       |

|---------------------------------------------------------------------|-------|

| 11.2.33. EP3 Endpoint 3 Control Register (EP3CON)                   | 11-32 |

| 11.2.34. Endpoint 3 Data Toggle Register (EP3TGL)                   |       |

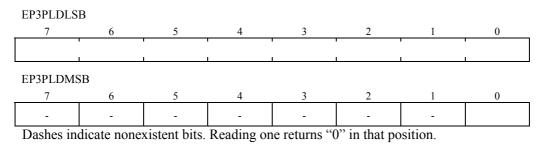

| 11.2.35. Endpoint 3 Payload Register Pair (EP3PLDLSB and EP3PLDMSB) | 11-33 |

| 11.2.36. Endpoint 0 FIFO Buffer Register (EP0RXFIFO/EP0TXFIFO)      | 11-34 |

| 11.2.37. Endpoint 1 FIFO Buffer Register (EP1RXFIFO/EP1TXFIFO)      | 11-34 |

| 11.2.38. Endpoint 2 FIFO Buffer Register (EP2RXFIFO/EP2TXFIFO)      | 11-34 |

| 11.2.39. Endpoint 3 FIFO Buffer Register (EP3RXFIFO/EP3TXFIFO)      | 11-35 |

| 11.2.40. Wake-up Control Register (AWKCON)                          |       |

| 11.3. Paired FIFO buffers Operation                                 |       |

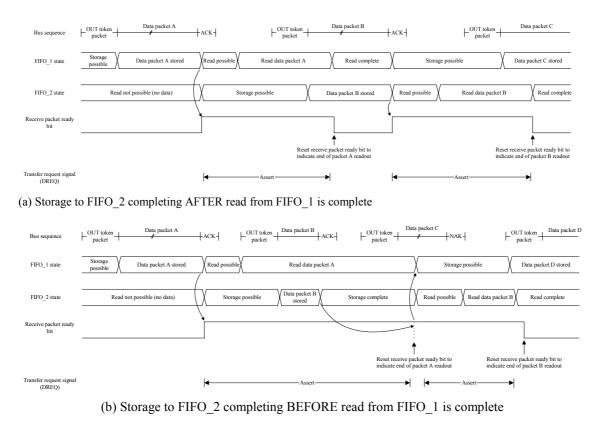

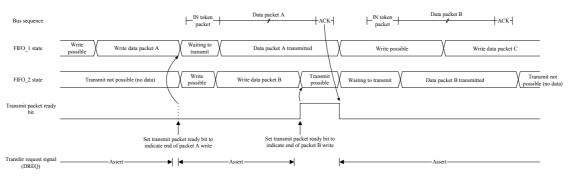

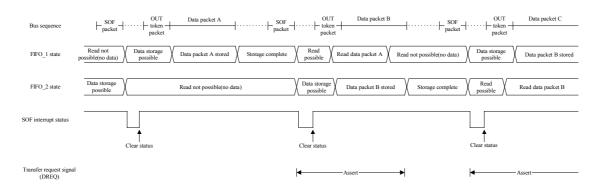

| 11.3.1. Bulk (Interrupt) Transfers                                  |       |

| 11.3.2. Isochronous Transfers                                       |       |

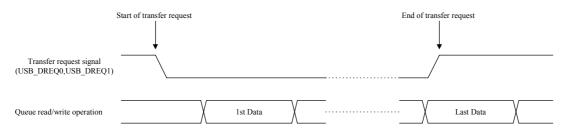

| 11.4. DMA Transfer Control                                          | 11-39 |

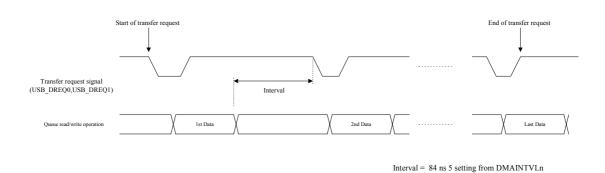

| 11.4.1. Transfer Request Conditions                                 | 11-39 |

| 11.4.2. Transfer Request Timing                                     |       |

| 11.5. Power Conservation Function                                   | 11-41 |

| 11.6. Usage Notes                                                   | 11-42 |

|                                                                     |       |

# Chapter 12 External Memory Controller (XMC)

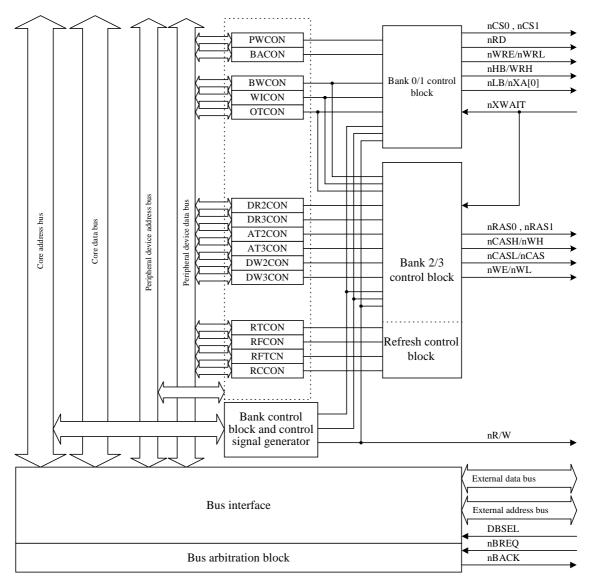

| 12.1.1.       Block Diagram.       12-3         12.1.2.       Pins       12-5         12.1.3.       Control Registers       12-5         12.1.4.       Address Space       12-7         12.2.       Detailed Control Register Descriptions       12-9         12.2.1.       Bus Width Control Register (WCON)       12-9         12.2.2.       WAIT Input Control Register (WCON)       12-10         12.2.3.       Off Time Control Register (OTCON)       12-11         12.2.4.       Programmable Wait Control Register (PWCON)       12-12         12.2.5.       Bus Access Control Register (BACON)       12-13         12.2.6.       DRAM Bank 2 Control Register (DR3CON)       12-14         12.2.7.       DRAM Bank 3 Control Register (DR3CON)       12-16         12.2.9.       DRAM Bank 3 Control Register (DR3CON)       12-16         12.2.9.       DRAM Bank 3 Access Timing Control Register (AT3CON)       12-16         12.2.10.       DRAM Bank 3 Programmable Wait Control Register (DW3CON)       12-17         12.2.11.       DRAM Bank 3 Programmable Wait Control Register (DW3CON)       12-17         12.2.12.       Refresh Timing Control Register (RTCON)       12-18         12.2.13.       Refresh Cycle Control Register (RTCON)       12-19                                                      | 12.1. Overview                                                   |       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------|

| 12.1.3.       Control Registers       12-6         12.1.4.       Address Space       12-7         12.2.       Detailed Control Register Descriptions       12-9         12.2.1.       Bus Width Control Register (WICON)       12-10         12.2.2.       WAIT Input Control Register (WICON)       12-11         12.2.3.       Off Time Control Register (OTCON)       12-11         12.2.4.       Programmable Wait Control Register (PWCON)       12-12         12.2.5.       Bus Access Control Register (DR3CON)       12-13         12.2.6.       DRAM Bank 2 Control Register (DR3CON)       12-16         12.2.9.       DRAM Bank 3 Control Register (DR3CON)       12-16         12.2.9.       DRAM Bank 3 Access Timing Control Register (AT2CON)       12-16         12.2.9.       DRAM Bank 3 Access Timing Control Register (DW2CON)       12-17         12.2.10.       DRAM Bank 3 Programmable Wait Control Register (DW3CON)       12-17         12.2.11.       DRAM Bank 3 Programmable Wait Control Register (DW3CON)       12-18         12.2.12.       Refresh Timer Counter (RFTCN)       12-18         12.2.13.       Refresh Timing Control Register (RCON)       12-19         12.2.14.       Refresh Timing Control Register (RCON)       12-19         12.2.15.       Refresh T                         | 12.1.1. Block Diagram                                            | 12-3  |

| 12.1.4.       Address Space       12-7         12.2.       Detailed Control Register Descriptions       12-9         12.2.1.       Bus Width Control Register (BWCON)       12-19         12.2.2.       WAIT Input Control Register (OTCON)       12-11         12.2.3.       Off Time Control Register (OTCON)       12-11         12.2.4.       Programmable Wait Control Register (PWCON)       12-12         12.2.5.       Bus Access Control Register (DR2CON)       12-13         12.2.6.       DRAM Bank 2 Control Register (DR3CON)       12-14         12.2.7.       DRAM Bank 3 Control Register (DR3CON)       12-16         12.2.8.       DRAM Bank 3 Control Register (AT2CON)       12-16         12.2.9.       DRAM Bank 3 Access Timing Control Register (AT3CON)       12-16         12.2.10.       DRAM Bank 3 Programmable Wait Control Register (DW2CON)       12-17         12.2.11.       DRAM Bank 3 Programmable Wait Control Register (DW3CON)       12-17         12.2.12.       Refresh Timer Counter (RFTCN)       12-18         12.2.13.       Refresh Control Register (RCON)       12-19         12.2.15.       Refresh Control Register (RFCON)       12-19         12.2.15.       Refresh Control Register (RFCON)       12-20         12.3.1.       Data Bus Width                               | 12.1.2. Pins                                                     | 12-5  |

| 12.2. Detailed Control Register Descriptions12-912.2.1. Bus Width Control Register (BWCON)12-912.2.2. WAIT Input Control Register (WICON)12-1012.2.3. Off Time Control Register (OTCON)12-1112.2.4. Programmable Wait Control Register (PWCON)12-1312.2.5. Bus Access Control Register (BACON)12-1412.2.7. DRAM Bank 2 Control Register (DR3CON)12-1412.2.8. DRAM Bank 3 Control Register (DR3CON)12-1612.2.9. DRAM Bank 3 Access Timing Control Register (AT2CON)12-1612.2.9. DRAM Bank 3 Access Timing Control Register (DW3CON)12-1712.2.10. DRAM Bank 3 Programmable Wait Control Register (DW3CON)12-1712.2.11. DRAM Bank 3 Programmable Wait Control Register (DW3CON)12-1812.2.12. Refresh Timer Counter (RFTCN)12-1812.2.13. Refresh Cycle Control Register (RCON)12-1912.2.14. Refresh Timing Control Register (RTCON)12-1812.2.15. Refresh Control Register (RFCON)12-1812.2.2.14. Refresh Timing Control Register (RTCON)12-1812.2.2.15. Refresh Control Register (RFCON)12-2012.3.1. Data Bus Width12-2212.3.2. Accessing Bank 0/1 External Memory Space12-2312.3.3. Accessing Bank 2/3 External Memory (DRAM) Space12-2612.3.3. Half-Word Access12-2612.3.3. Wait Cycles12-2612.3.3. Wait Cycles12-2612.3.3. Half-Word Access12-2812.3.3. Half-Word Access12-2812.3.3. Kait Cycles12-2812.3.3. Half-Word Access12-28< | 12.1.3. Control Registers                                        | 12-6  |

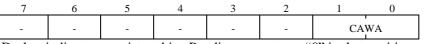

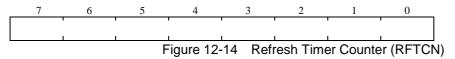

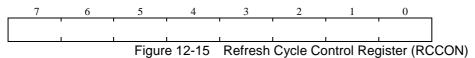

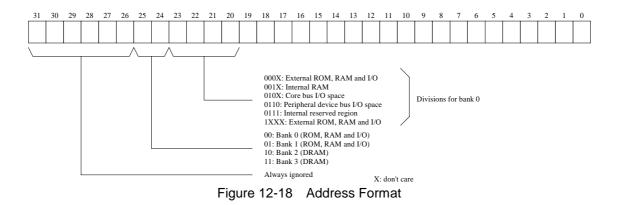

| 12.2.1. Bus Width Control Register (BWCON)12-912.2.2. WAIT Input Control Register (WICON)12-1012.2.3. Off Time Control Register (OTCON)12-1112.2.4. Programmable Wait Control Register (PWCON)12-1212.2.5. Bus Access Control Register (BACON)12-1312.2.6. DRAM Bank 2 Control Register (DR3CON)12-1412.2.7. DRAM Bank 3 Control Register (DR3CON)12-1612.2.9. DRAM Bank 3 Access Timing Control Register (AT2CON)12-1612.2.10. DRAM Bank 2 Programmable Wait Control Register (DW2CON)12-1712.2.11. DRAM Bank 3 Programmable Wait Control Register (DW2CON)12-1712.2.12. Refresh Timer Counter (RFTCN)12-1812.2.13. Refresh Cycle Control Register (RCCON)12-1812.2.14. Refresh Timing Control Register (RTCON)12-1912.2.15. Refresh Control Register (RFCON)12-1212.3.1. Data Bus Width12-2212.3.2. Accessing Bank 0/1 External Memory Space12-2312.3.2.1. Basic Access12-2412.3.3. Accessing Bank 2/3 External Memory (DRAM) Space12-2612.3.3. Address Multiplexing12-2612.3.3. Address Multiplexing12-2612.3.3.4. Half-Word Access12-2812.3.3.4. Half-Word Access12-2812.3.3.4. Half-Word Access12-2812.3.3.4. Half-Word Access12-2312.3.3.5. Fast page (Burst) Access12-33                                                                                                                                                    | 12.1.4. Address Space                                            | 12-7  |

| 12.2.2.WAIT Input Control Register (WICON)12-1012.2.3.Off Time Control Register (OTCON)12-1112.2.4.Programmable Wait Control Register (PWCON)12-1212.2.5.Bus Access Control Register (BACON)12-1312.2.6.DRAM Bank 2 Control Register (DR2CON)12-1412.2.7.DRAM Bank 3 Control Register (DR3CON)12-1512.2.8.DRAM Bank 2 Access Timing Control Register (AT2CON)12-1612.2.9.DRAM Bank 3 Access Timing Control Register (AT3CON)12-1612.2.10.DRAM Bank 3 Programmable Wait Control Register (DW2CON)12-1712.2.11.DRAM Bank 3 Programmable Wait Control Register (DW3CON)12-1712.2.12.Refresh Timer Counter (RFTCN)12-1812.2.13.Refresh Cycle Control Register (RTCON)12-1812.2.14.Refresh Timing Control Register (RTCON)12-1012.3.Accessing Address Space12-2212.3.1.Data Bus Width12-2212.3.2.Accessing Bank 0/1 External Memory Space12-2312.3.3.Half-Word Access12-2612.3.3.Adcress Multiplexing12-2612.3.3.Adcress Multiplexing12-2612.3.3.Half-Word Access12-2712.3.3.Half-Word Access12-2812.3.3.Half-Word Access12-2812.3.3.Half-Word Access12-2312.3.3.Katternal Memory (DRAM) Space12-2612.3.3.Half-Word Access12-2812.3.3.Half-Word Access12-23 </td <td></td> <td></td>                                                                                                                                                    |                                                                  |       |

| 12.2.3. Off Time Control Register (OTCON)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                  |       |

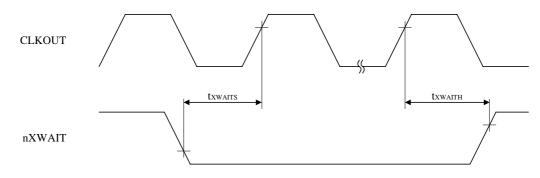

| 12.2.4. Programmable Wait Control Register (PWCON)12-1212.2.5. Bus Access Control Register (BACON)12-1312.2.6. DRAM Bank 2 Control Register (DR2CON)12-1412.2.7. DRAM Bank 3 Control Register (DR3CON)12-1512.2.8. DRAM Bank 2 Access Timing Control Register (AT2CON)12-1612.2.9. DRAM Bank 3 Access Timing Control Register (AT3CON)12-1612.2.10. DRAM Bank 3 Programmable Wait Control Register (DW2CON)12-1712.2.11. DRAM Bank 3 Programmable Wait Control Register (DW3CON)12-1812.2.12. Refresh Timer Counter (RFTCN)12-1812.2.13. Refresh Cycle Control Register (RTCON)12-1912.2.14. Refresh Timing Control Register (RTCON)12-1912.2.15. Refresh Control Register (RFCON)12-2012.3. Accessing Address Space12-2212.3.1. Data Bus Width12-2212.3.2. Wait Cycles12-2312.3.2. Wait Cycles12-2412.3.3. Accessing Bank 0/1 External Memory Space12-2312.3.3. Accessing Bank 2/3 External Memory (DRAM) Space12-2612.3.3.1. Address Multiplexing12-2612.3.3.2. Basic Access12-2612.3.3.4. Half-Word Access12-2612.3.3.4. Half-Word Access12-2612.3.3.5. Fast page (Burst) Access12-33                                                                                                                                                                                                                                           | 12.2.2. WAIT Input Control Register (WICON)                      |       |

| 12.2.5. Bus Access Control Register (BACON)12-1312.2.6. DRAM Bank 2 Control Register (DR2CON)12-1412.2.7. DRAM Bank 3 Control Register (DR3CON)12-1512.2.8. DRAM Bank 2 Access Timing Control Register (AT2CON)12-1612.2.9. DRAM Bank 3 Access Timing Control Register (AT3CON)12-1612.2.10. DRAM Bank 3 Programmable Wait Control Register (DW2CON)12-1712.2.11. DRAM Bank 3 Programmable Wait Control Register (DW3CON)12-1712.2.12. Refresh Timer Counter (RFTCN)12-1812.2.13. Refresh Cycle Control Register (RCCON)12-1912.2.14. Refresh Timing Control Register (RTCON)12-1912.2.15. Refresh Control Register (RFCON)12-2012.3. Accessing Address Space12-2212.3.1. Data Bus Width12-2212.3.2. Accessing Bank 0/1 External Memory Space12-2312.3.2.1. Basic Access12-2412.3.2.3. Address Multiplexing12-2612.3.3.1. Address Multiplexing12-2612.3.3.2. Basic Access12-2612.3.3.3. Wait Cycles12-2712.3.3.4. Half-Word Access12-2812.3.3.5. Fast page (Burst) Access12-33                                                                                                                                                                                                                                                                                                                                                     |                                                                  |       |

| 12.2.6. DRAM Bank 2 Control Register (DR2CON)12-1412.2.7. DRAM Bank 3 Control Register (DR3CON)12-1512.2.8. DRAM Bank 2 Access Timing Control Register (AT2CON)12-1612.2.9. DRAM Bank 3 Access Timing Control Register (AT3CON)12-1612.2.10. DRAM Bank 2 Programmable Wait Control Register (DW2CON)12-1712.2.11. DRAM Bank 3 Programmable Wait Control Register (DW3CON)12-1712.2.12. Refresh Timer Counter (RFTCN)12-1812.2.13. Refresh Cycle Control Register (RCCON)12-1912.2.14. Refresh Timing Control Register (RTCON)12-1912.2.15. Refresh Control Register (RFCON)12-2012.3. Accessing Address Space12-2212.3.1. Data Bus Width12-2212.3.2. Accessing Bank 0/1 External Memory Space12-2312.3.2.1. Basic Access12-2512.3.3. Accessing Bank 2/3 External Memory (DRAM) Space12-2612.3.3.1. Address Multiplexing12-2612.3.3.2. Basic Access12-2612.3.3.3. Wait Cycles12-2612.3.3.4. Half-Word Access12-2712.3.3.5. Fast page (Burst) Access12-33                                                                                                                                                                                                                                                                                                                                                                            | 12.2.4. Programmable Wait Control Register (PWCON)               | 12-12 |

| 12.2.7. DRAM Bank 3 Control Register (DR3CON)       12-15         12.2.8. DRAM Bank 2 Access Timing Control Register (AT2CON)       12-16         12.2.9. DRAM Bank 3 Access Timing Control Register (AT3CON)       12-16         12.2.10. DRAM Bank 2 Programmable Wait Control Register (DW2CON)       12-17         12.2.11. DRAM Bank 3 Programmable Wait Control Register (DW3CON)       12-17         12.2.12. Refresh Timer Counter (RFTCN)       12-18         12.2.13. Refresh Cycle Control Register (RCCON)       12-19         12.2.15. Refresh Control Register (RTCON)       12-19         12.2.15. Refresh Control Register (RFCON)       12-20         12.3. Accessing Address Space       12-22         12.3.1. Data Bus Width       12-22         12.3.2.2. Wait Cycles       12-24         12.3.2.3. Half-Word Access       12-25         12.3.3.1. Address Multiplexing       12-26         12.3.3.2. Basic Access       12-26         12.3.3.3. Wait Cycles       12-27         12.3.3.4. Half-Word Access       12-26         12.3.3.4. Half-Word Access       12-28         12.3.3.5. Fast page (Burst) Access       12-33                                                                                                                                                                                  | 12.2.5. Bus Access Control Register (BACON)                      | 12-13 |

| 12.2.8. DRAM Bank 2 Access Timing Control Register (AT2CON).12-1612.2.9. DRAM Bank 3 Access Timing Control Register (AT3CON).12-1612.2.10. DRAM Bank 2 Programmable Wait Control Register (DW2CON)12-1712.2.11. DRAM Bank 3 Programmable Wait Control Register (DW3CON)12-1712.2.12. Refresh Timer Counter (RFTCN)12-1812.2.13. Refresh Cycle Control Register (RCCON)12-1912.2.14. Refresh Timing Control Register (RTCON)12-1912.2.15. Refresh Control Register (RFCON)12-2012.3. Accessing Address Space12-2212.3.1. Data Bus Width12-2212.3.2.2. Wait Cycles12-2312.3.2.3. Half-Word Access12-2512.3.3.1. Address Multiplexing12-2612.3.3.2. Basic Access12-2612.3.3.3. Wait Cycles12-2712.3.3.4. Half-Word Access12-2812.3.3.5. Fast page (Burst) Access12-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 12.2.6. DRAM Bank 2 Control Register (DR2CON)                    | 12-14 |

| 12.2.9. DRAM Bank 3 Access Timing Control Register (AT3CON)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                  |       |

| 12.2.9. DRAM Bank 3 Access Timing Control Register (AT3CON)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12.2.8. DRAM Bank 2 Access Timing Control Register (AT2CON)      | 12-16 |

| 12.2.11. DRAM Bank 3 Programmable Wait Control Register (DW3CON)       12-17         12.2.12. Refresh Timer Counter (RFTCN)       12-18         12.2.13. Refresh Cycle Control Register (RCCON)       12-18         12.2.14. Refresh Timing Control Register (RTCON)       12-19         12.2.15. Refresh Control Register (RFCON)       12-20         12.3. Accessing Address Space       12-22         12.3.1. Data Bus Width       12-22         12.3.2.2. Accessing Bank 0/1 External Memory Space       12-23         12.3.2.3. Half-Word Access       12-24         12.3.3. Accessing Bank 2/3 External Memory (DRAM) Space       12-26         12.3.3.1. Address Multiplexing       12-26         12.3.3.3. Wait Cycles       12-27         12.3.3.4. Half-Word Access       12-27         12.3.3.5. Fast page (Burst) Access       12-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                  |       |

| 12.2.12. Refresh Timer Counter (RFTCN)       12-18         12.2.13. Refresh Cycle Control Register (RCCON)       12-18         12.2.14. Refresh Timing Control Register (RTCON)       12-19         12.2.15. Refresh Control Register (RFCON)       12-20         12.3. Accessing Address Space       12-22         12.3.1. Data Bus Width       12-22         12.3.2. Accessing Bank 0/1 External Memory Space       12-23         12.3.2.1. Basic Access       12-24         12.3.2.2. Wait Cycles       12-24         12.3.3. Half-Word Access       12-25         12.3.3.1. Address Multiplexing       12-26         12.3.3.2. Basic Access       12-26         12.3.3.3. Wait Cycles       12-26         12.3.3.4. Half-Word Access       12-27         12.3.3.5. Fast page (Burst) Access       12-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12.2.10. DRAM Bank 2 Programmable Wait Control Register (DW2CON) | 12-17 |

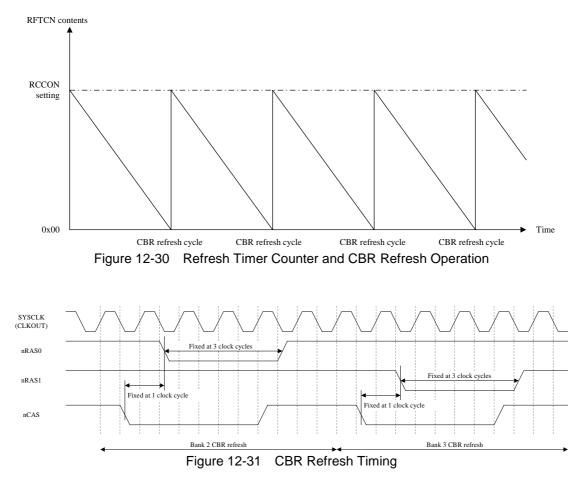

| 12.2.13. Refresh Cycle Control Register (RCCON)       12-18         12.2.14. Refresh Timing Control Register (RTCON)       12-19         12.2.15. Refresh Control Register (RFCON)       12-20         12.3. Accessing Address Space       12-22         12.3.1. Data Bus Width       12-22         12.3.2. Accessing Bank 0/1 External Memory Space       12-23         12.3.2.1. Basic Access       12-23         12.3.2.2. Wait Cycles       12-24         12.3.3. Accessing Bank 2/3 External Memory (DRAM) Space       12-26         12.3.3.1. Address Multiplexing       12-26         12.3.3.2. Basic Access       12-26         12.3.3.3. Wait Cycles       12-26         12.3.3.4. Half-Word Access       12-27         12.3.3.5. Fast page       (Burst) Access       12-28         12.3.3.5. Fast page       (Burst) Access       12-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 12.2.11. DRAM Bank 3 Programmable Wait Control Register (DW3CON) | 12-17 |

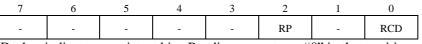

| 12.2.14. Refresh Timing Control Register (RTCON)       12-19         12.2.15. Refresh Control Register (RFCON)       12-20         12.3. Accessing Address Space       12-22         12.3.1. Data Bus Width       12-22         12.3.2. Accessing Bank 0/1 External Memory Space       12-23         12.3.2.1. Basic Access       12-23         12.3.2.2. Wait Cycles       12-24         12.3.3. Accessing Bank 2/3 External Memory (DRAM) Space       12-26         12.3.3.1. Address Multiplexing       12-26         12.3.3.2. Basic Access       12-26         12.3.3.3. Wait Cycles       12-26         12.3.3.4. Half-Word Access       12-27         12.3.3.5. Fast page       (Burst) Access       12-28         12.3.3.5. Fast page       (Burst) Access       12-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                  |       |

| 12.2.15. Refresh Control Register (RFCON).       12-20         12.3. Accessing Address Space       12-22         12.3.1. Data Bus Width       12-22         12.3.2. Accessing Bank 0/1 External Memory Space       12-23         12.3.2.1. Basic Access       12-23         12.3.2.2. Wait Cycles       12-24         12.3.3. Accessing Bank 2/3 External Memory (DRAM) Space       12-26         12.3.3.1. Address Multiplexing       12-26         12.3.3.2. Basic Access       12-27         12.3.3.3. Wait Cycles       12-26         12.3.3.4. Half-Word Access       12-27         12.3.3.5. Fast page       (Burst) Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12.2.13. Refresh Cycle Control Register (RCCON)                  | 12-18 |

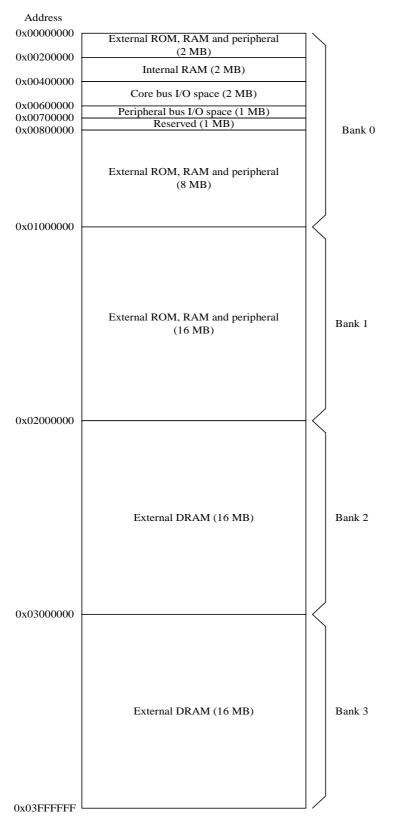

| 12.3. Accessing Address Space       12-22         12.3.1. Data Bus Width       12-22         12.3.2. Accessing Bank 0/1 External Memory Space       12-23         12.3.2.1. Basic Access       12-23         12.3.2.2. Wait Cycles       12-24         12.3.2.3. Half-Word Access       12-25         12.3.3. Accessing Bank 2/3 External Memory (DRAM) Space       12-26         12.3.3.1. Address Multiplexing       12-26         12.3.3.2. Basic Access       12-27         12.3.3.3. Wait Cycles       12-27         12.3.3.4. Half-Word Access       12-28         12.3.3.5. Fast page       (Burst) Access       12-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12.2.14. Refresh Timing Control Register (RTCON)                 | 12-19 |

| 12.3.1. Data Bus Width       12-22         12.3.2. Accessing Bank 0/1 External Memory Space       12-23         12.3.2.1. Basic Access       12-23         12.3.2.2. Wait Cycles       12-24         12.3.2.3. Half-Word Access       12-25         12.3.3. Accessing Bank 2/3 External Memory (DRAM) Space       12-26         12.3.3.1. Address Multiplexing       12-26         12.3.3.2. Basic Access       12-27         12.3.3.3. Wait Cycles       12-27         12.3.3.4. Half-Word Access       12-28         12.3.3.5. Fast page       (Burst) Access       12-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12.2.15. Refresh Control Register (RFCON)                        |       |

| 12.3.2. Accessing Bank 0/1 External Memory Space       12-23         12.3.2.1. Basic Access       12-23         12.3.2.2. Wait Cycles       12-24         12.3.2.3. Half-Word Access       12-25         12.3.3. Accessing Bank 2/3 External Memory (DRAM) Space       12-26         12.3.3.1. Address Multiplexing       12-26         12.3.3.2. Basic Access       12-27         12.3.3.3. Wait Cycles       12-28         12.3.3.4. Half-Word Access       12-32         12.3.3.5. Fast page       (Burst) Access       12-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 12.3. Accessing Address Space                                    |       |

| 12.3.2.1. Basic Access       12-23         12.3.2.2. Wait Cycles       12-24         12.3.2.3. Half-Word Access       12-25         12.3.3. Accessing Bank 2/3 External Memory (DRAM) Space       12-26         12.3.3.1. Address Multiplexing       12-26         12.3.3.2. Basic Access       12-27         12.3.3.3. Wait Cycles       12-28         12.3.3.4. Half-Word Access       12-32         12.3.3.5. Fast page       (Burst) Access       12-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                  |       |

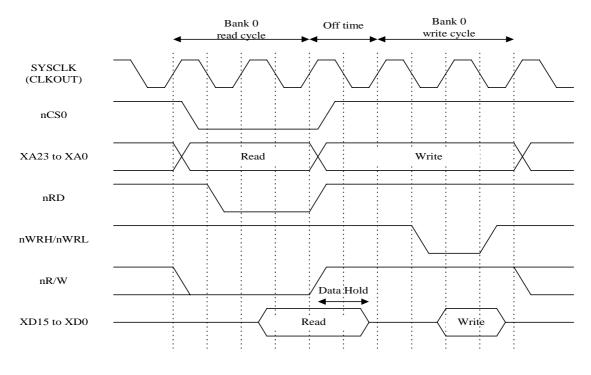

| 12.3.2.1. Basic Access       12-23         12.3.2.2. Wait Cycles       12-24         12.3.2.3. Half-Word Access       12-25         12.3.3. Accessing Bank 2/3 External Memory (DRAM) Space       12-26         12.3.3.1. Address Multiplexing       12-26         12.3.3.2. Basic Access       12-27         12.3.3.3. Wait Cycles       12-28         12.3.3.4. Half-Word Access       12-32         12.3.3.5. Fast page       (Burst) Access       12-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12.3.2. Accessing Bank 0/1 External Memory Space                 |       |

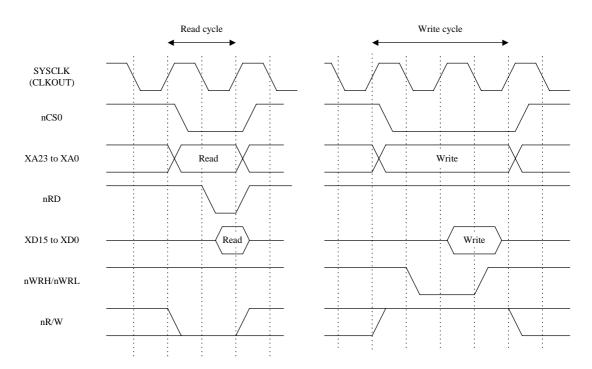

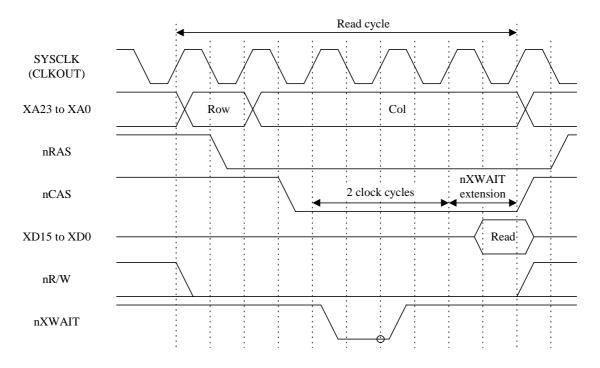

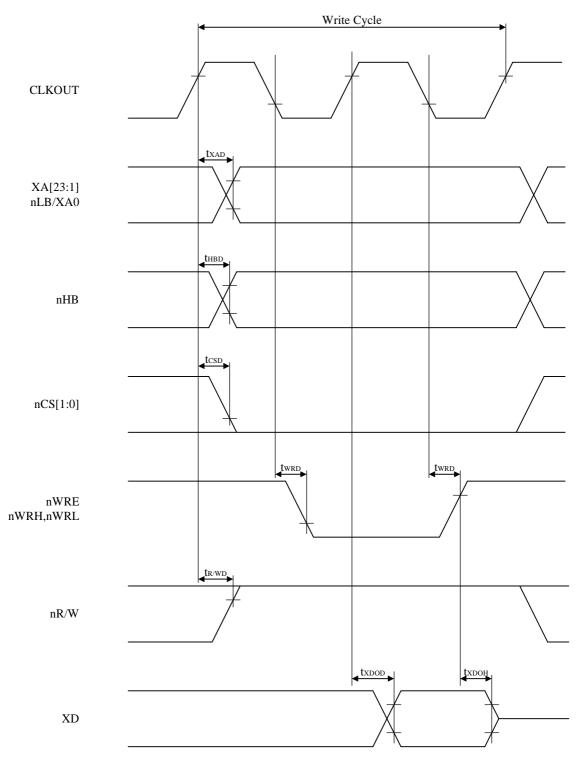

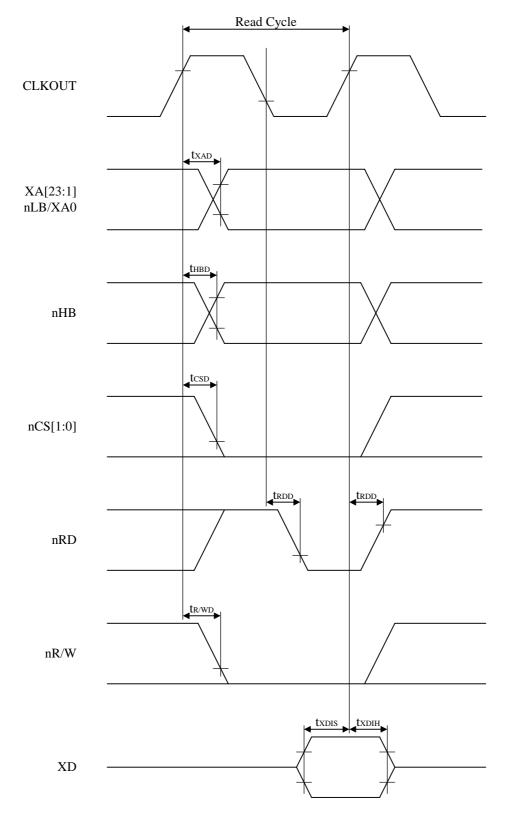

| 12.3.2.3. Half-Word Access.       12-25         12.3.3. Accessing Bank 2/3 External Memory (DRAM) Space       12-26         12.3.3.1. Address Multiplexing       12-26         12.3.3.2. Basic Access       12-27         12.3.3.3. Wait Cycles       12-28         12.3.3.4. Half-Word Access       12-32         12.3.5. Fast page       (Burst) Access       12-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 12.3.2.1. Basic Access                                           |       |

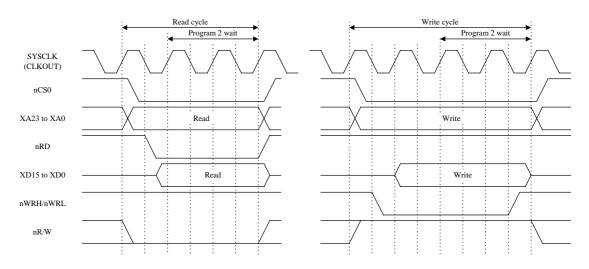

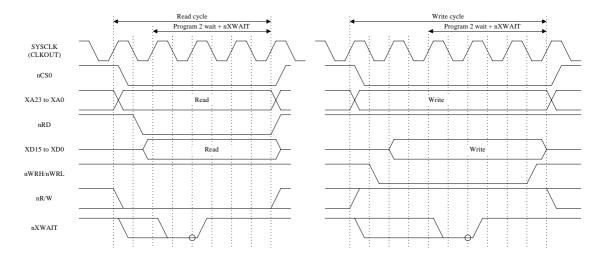

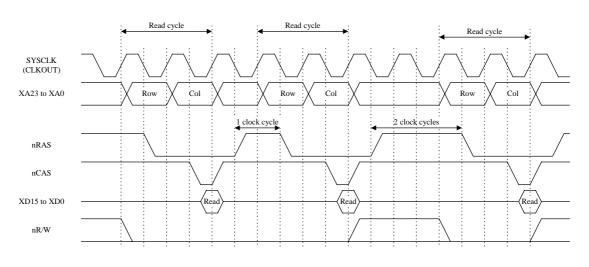

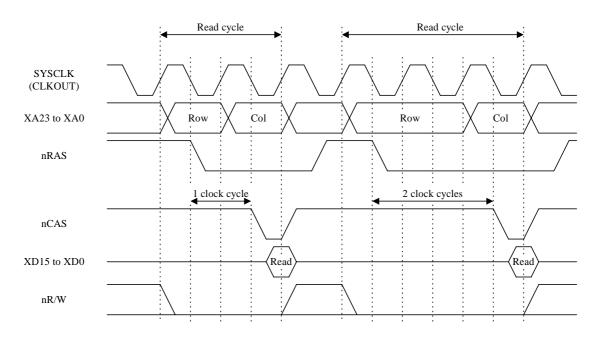

| 12.3.3. Accessing Bank 2/3 External Memory (DRAM) Space       12-26         12.3.3.1. Address Multiplexing       12-26         12.3.3.2. Basic Access       12-27         12.3.3.3. Wait Cycles       12-28         12.3.3.4. Half-Word Access       12-32         12.3.3.5. Fast page       (Burst) Access       12-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 12.3.2.2. Wait Cycles                                            |       |

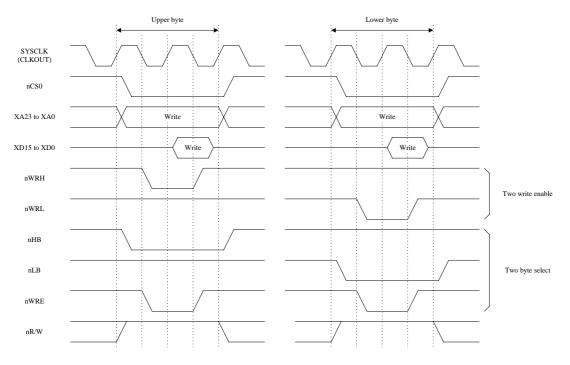

| 12.3.3.1. Address Multiplexing.       12-26         12.3.3.2. Basic Access       12-27         12.3.3.3. Wait Cycles       12-28         12.3.3.4. Half-Word Access       12-32         12.3.3.5. Fast page       (Burst) Access       12-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12.3.2.3. Half-Word Access                                       |       |

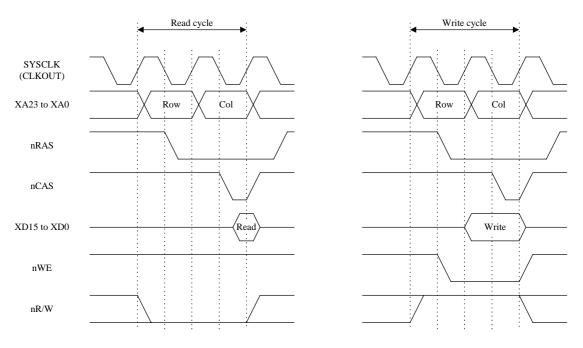

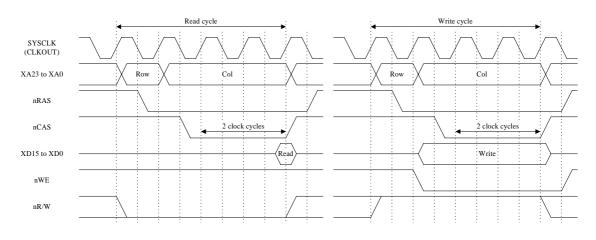

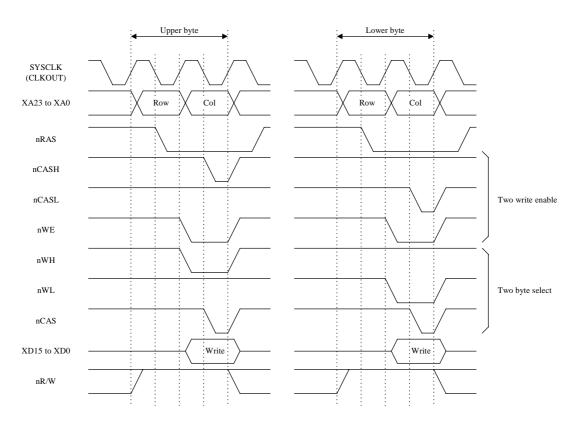

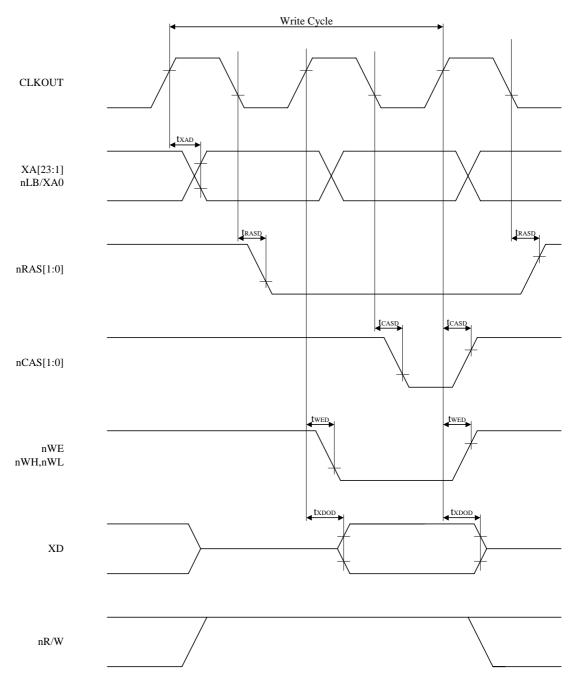

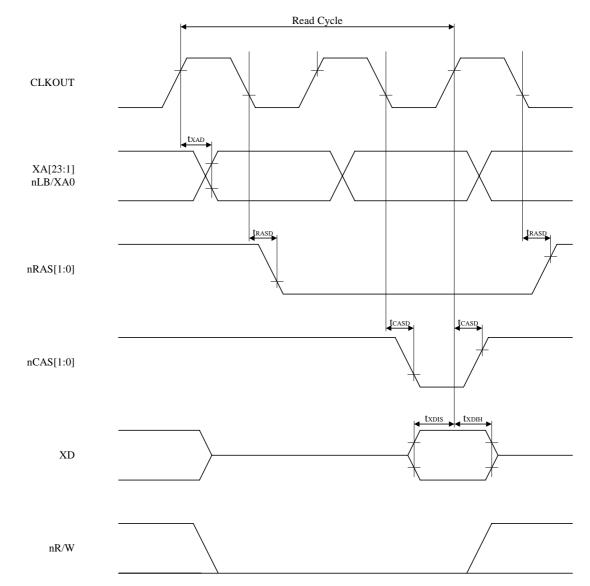

| 12.3.3.2. Basic Access       12-27         12.3.3.3. Wait Cycles       12-28         12.3.3.4. Half-Word Access       12-32         12.3.3.5. Fast page       (Burst) Access         12-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12.3.3. Accessing Bank 2/3 External Memory (DRAM) Space          | 12-26 |

| 12.3.3.3. Wait Cycles       12-28         12.3.3.4. Half-Word Access       12-32         12.3.3.5. Fast page       (Burst) Access         12-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 12.3.3.1. Address Multiplexing                                   |       |

| 12.3.3.4. Half-Word Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12.3.3.2. Basic Access                                           |       |

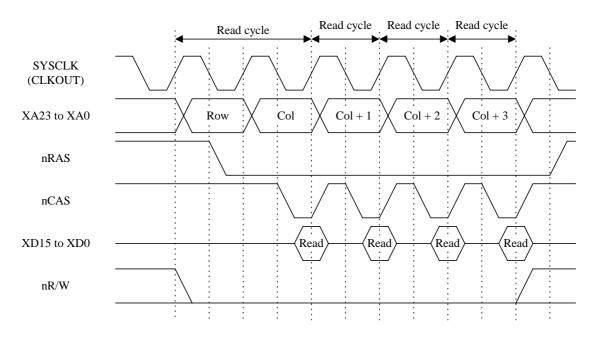

| 12.3.3.5. Fast page (Burst) Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 12.3.3.3. Wait Cycles                                            |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                  |       |

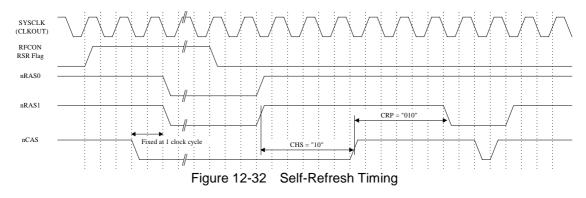

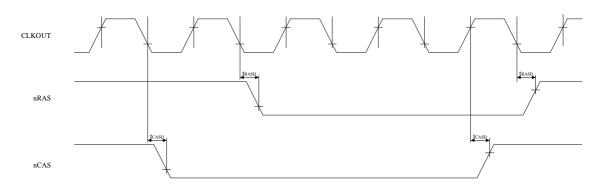

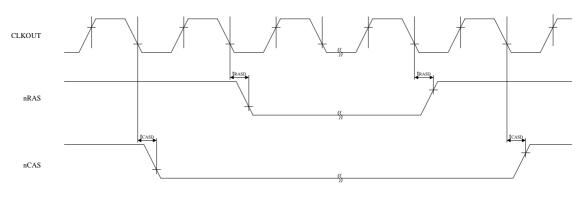

| 12.3.3.6. Refresh Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                  |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 12.3.3.6. Refresh Access                                         |       |

| 12.3.4. | External Memory Space Access for All Banks      |  |

|---------|-------------------------------------------------|--|

| 12.3.4  | 1. Off Time Control                             |  |

| 12.3.4  | 2. Store Buffer                                 |  |

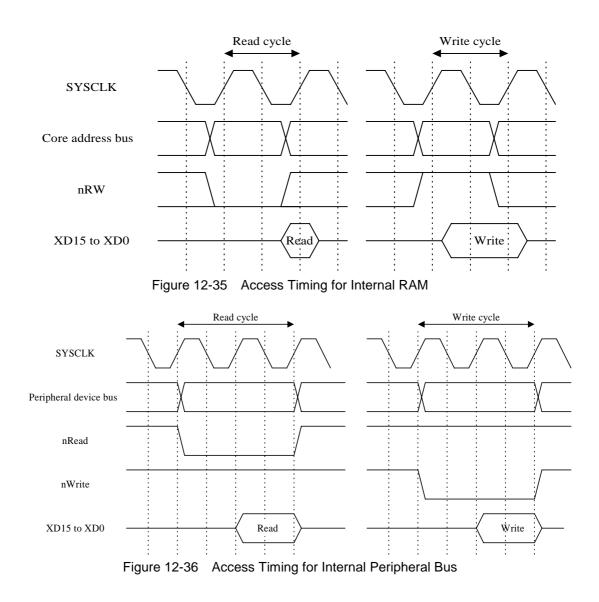

| 12.3.5. | Accessing Bank 0 Internal Memory Space          |  |

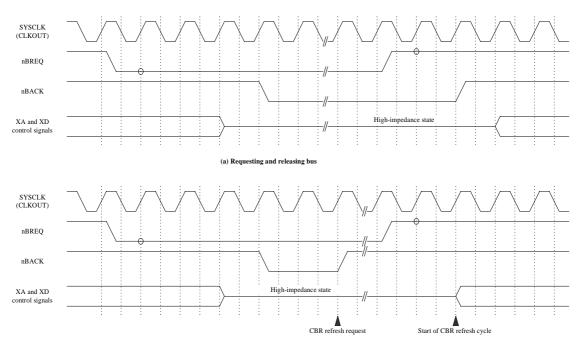

|         | s Arbitration                                   |  |

| 12.4.1. | Bus Access Priority                             |  |

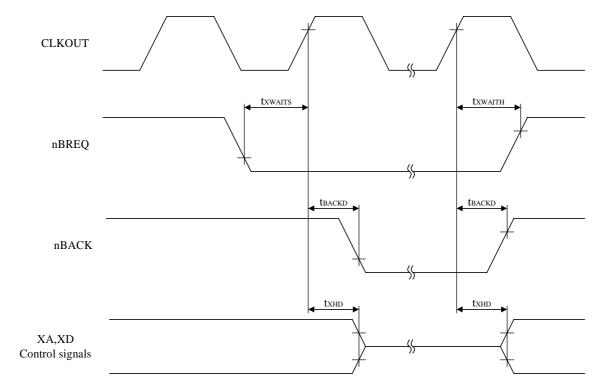

|         | Requesting and obtaining Access to External Bus |  |

|         | Bus Lock Operation                              |  |

|         | ndby Modes                                      |  |

|         | Shifting to HALT Mode                           |  |

| 12.5.2. | Shifting to STOP Mode                           |  |

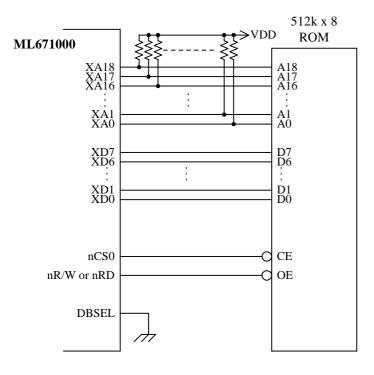

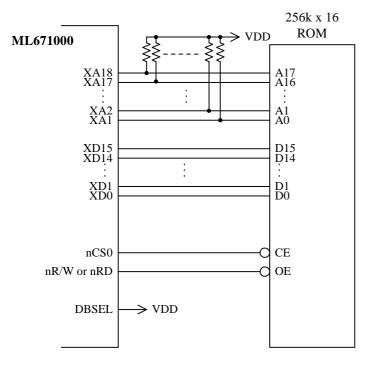

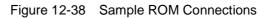

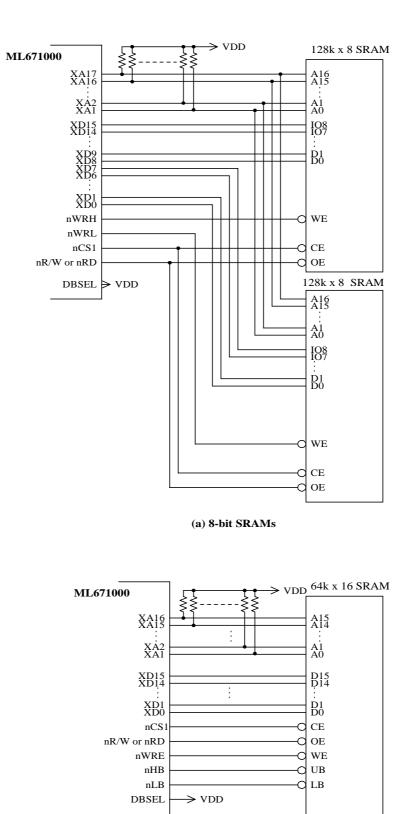

|         | nnecting External Memory                        |  |

| 12.6.1. | Connecting ROM                                  |  |

|         | Connecting SRAM                                 |  |

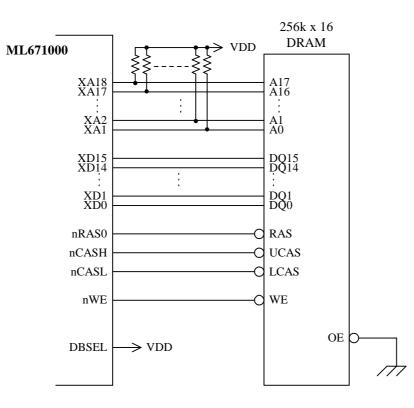

|         | Connecting DRAM                                 |  |

|         |                                                 |  |

## Chapter 13 Electrical Characteristics

| 13-2  |

|-------|

|       |

| 13-3  |

| 13-4  |

| 13-4  |

| 13-4  |

| 13-5  |

| 13-6  |

| 13-6  |

| 13-7  |

| 13-8  |

| 13-8  |

| 13-9  |

| 13-10 |

| 13-11 |

|       |

| 13-13 |

| 13-13 |

| 13-14 |

|       |

# Appendix

| A. List of Control Registers     | A-2  |

|----------------------------------|------|

| B. Sample Circuits               |      |

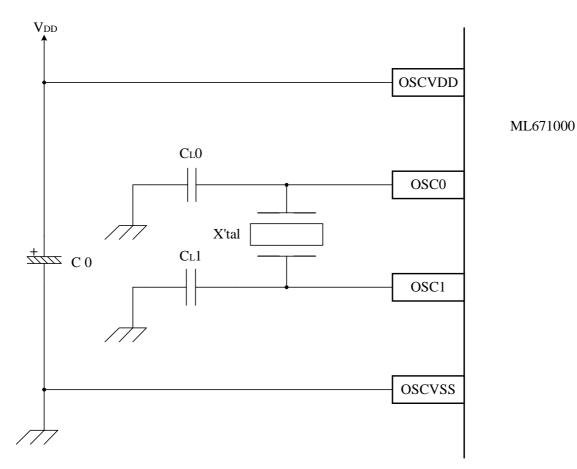

| B.1. Crystal Oscillation circuit |      |

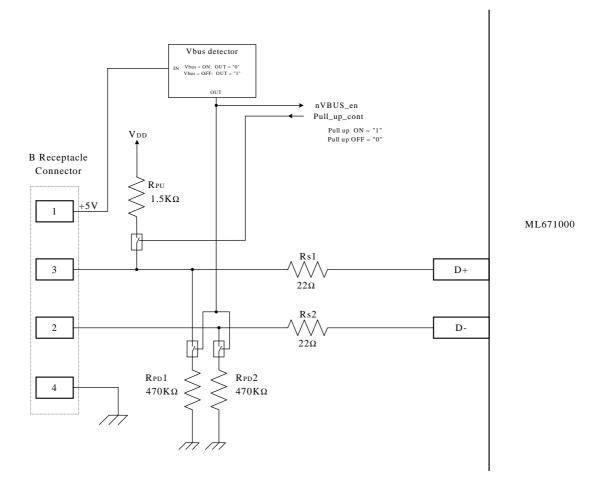

| B.2. USB Interface Circuit       |      |

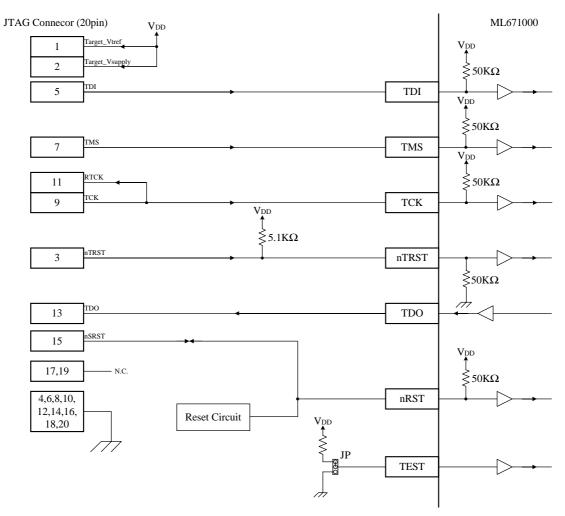

| B.3. JTAG Interface Circuit      | A-10 |

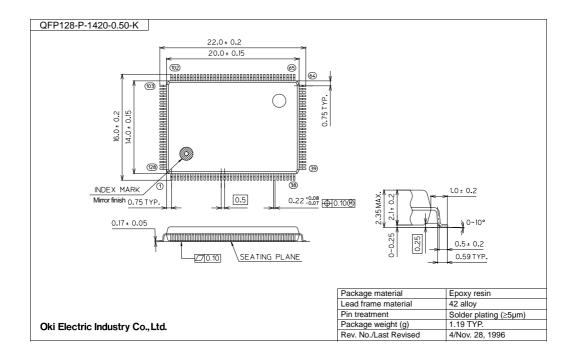

| C. Package Dimensions            |      |

|                                  |      |

# Chapter 1 Overview

## **1.1. Features**

This high-performance 32-bit single-chip microcontroller combines a 32-bit ARM7TDMI RISC CPU core developed by ARM Limited with such peripheral functions as USB device controller, DMA controller (DMAC), universal asynchronous receiver transmitter (UART), serial communications interface, and 16-bit timers. It therefore offers a highly optimized combination of 32-bit data processing capabilities, built-in memory, and on-chip peripherals for controlling PC peripherals and communications devices. A built-in external memory controller (XMC) supports direct connection to memory—SRAM and DRAM, for example—and peripheral devices for adding even more functionality.

The following is a list of features.

- CPU

- 32-bit RISC CPU core (ARM7TDMI)

- Two instruction sets: Rich set of 32-bit ARM instructions and a subset, the 16-bit Thumb instructions, offering higher code efficiency.

- 29 32-bit general-purpose registers

- Built-in multiplication unit

- Internal Memory

- 4 kilobytes of RAM

- I/O Ports

- 64 individually configurable, bidirectional I/O pins

- Timers

- Two flexible 16-bit timers offering a choice of four operation modes: auto reload timer (ART), compare out (CMO), pulse width modulation (PWM), or capture input (CAP)

- Two general-purpose 16-bit auto reload timers

- Universal Asynchronous Receiver/Transmitter (UART)

- Functionally equivalent to the 16550A, this block includes 16-byte FIFO buffers for both transmit and receive and a built-in baud rate generator.

- Serial Communications Interface (SCI)

- This supports two communications modes: asynchronous (UART) and clock synchronous. It includes a built-in baud rate generator.

- USB Device Controller (USBC)

- Full-speed (12 Mbps) operation compliant with USB 1.1.

- Transfer types: Control, bulk, isochronous, and interrupt

- Four bidirectional endpoints with the following buffers

Endpoint 0 64 bytes each for transmit and receive

Endpoint 1 64 bytes×1 (bidirectional)

Endpoint 2 64 bytes×2 (bidirectional, alternating)

Endpoint 3 256 bytes×2 (bidirectional, alternating)

- DMA Controller (DMAC)

- Two channels

- Single and dual addressing

- Cycle steal and burst transfers

- 8- and 16-bit data transfers

- Maximum number of data items per transfer: 65,536

- Addressing space: 64 megabytes

- Interrupt Controller

- Maximum of 22 interrupt sources

- One external fast interrupt request (FIQ)

- Eight external interrupts

- Thirteen internal interrupts

- Interrupt sources are assigned one of eight priority levels.

- External Memory Controller (XMC)

- Direct connection of ROM, SRAM, DRAM, and external peripheral devices

- Memory control for four banks: Two for ROM, RAM, or peripheral devices; two for DRAM

- Separate wait control and other parameters for each bank

- Bus arbitration

- Clock generator

- Built-in crystal oscillator circuit

- Built-in ×4 phase-locked loop (PLL) allowing a single 12-MHz crystal oscillator to supply both a 48-MHz clock signal to the USB device controller and a 24-MHz (max.) one to the CPU and the built-in peripheral devices Clock gear shifting for switching operating clock frequency with processing load over fourfold range: ×1/2, ×1, ×2

- Time Base Generator (TBG)

- Time base clock supplies for built-in peripheral devices

- 12-bit watchdog timer

- Standby Functions

- HALT and STOP modes

- Onboard debugging function

- JTAG interface allowing onboard debugging

- Package: 128 pin QFP

## 1.2. Block Diagram

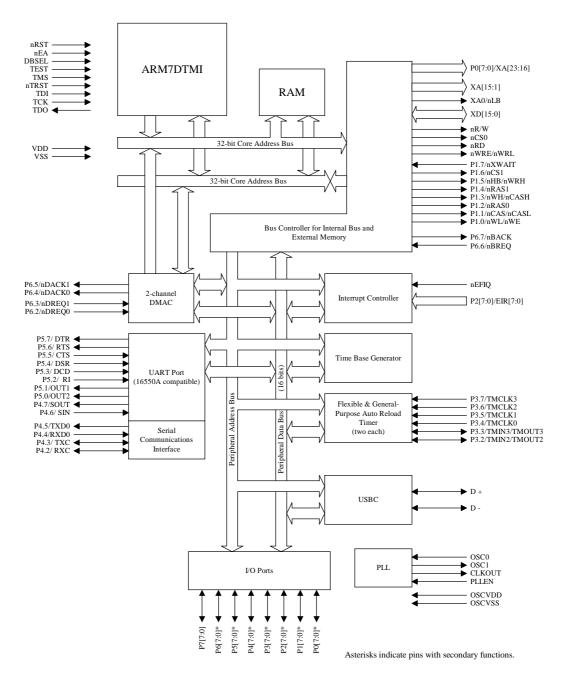

Figure 1-1 gives a block diagram for this LSI.

Figure 1-1 ML671000 Block Diagram

## **1.3.** Pins

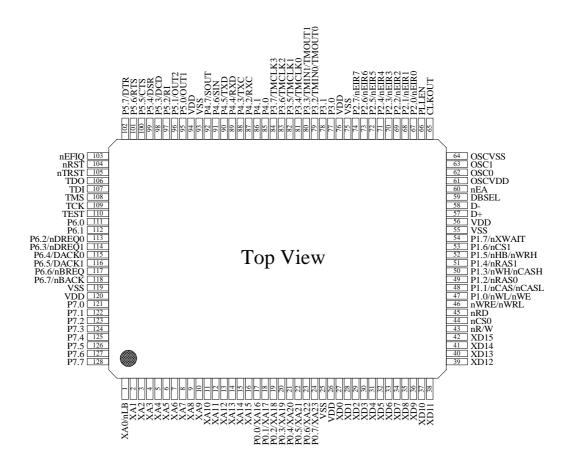

Figure 1-2 shows the pin assignments for this LSI.

Figure 1-2 Pin Assignments

# **1.3.1.** Pin Descriptions

Table 1-1 summarizes pin functions.

| Туре              | Pin Name      | Number        | I/O<br>Direction | Primary/<br>secondary | Description                                                                                                 |

|-------------------|---------------|---------------|------------------|-----------------------|-------------------------------------------------------------------------------------------------------------|

| A                 | XA15 to XA1   | 16 to 2       | 0                | -                     | External address bus bits 15 to 1                                                                           |